1125 Kasli-SoC #70

155

1125.tex

Normal file

@ -0,0 +1,155 @@

|

||||

\input{preamble}

|

||||

\input{shared/coredevice}

|

||||

\graphicspath{{images/1125}{images}}

|

||||

|

||||

\title{1125 Carrier Kasli-SoC}

|

||||

\author{M-Labs Limited}

|

||||

\date{December 2024}

|

||||

\revision{Revision 0} % WIP

|

||||

\companylogo{\includegraphics[height=0.73in]{artiq_sinara.pdf}}

|

||||

|

||||

\begin{document}

|

||||

\maketitle

|

||||

|

||||

\section{Features}

|

||||

|

||||

\begin{itemize}

|

||||

\item{RJ45 10/100/1000T Ethernet connector}

|

||||

\item{4 SFP 6Gb/s slots for DRTIO}

|

||||

|

architeuthis marked this conversation as resolved

Outdated

|

||||

\item{12 EEM ports for daughtercards}

|

||||

\item{Xilinx Zynq-7 SoC with Kintex-7 FPGA}

|

||||

|

architeuthis marked this conversation as resolved

Outdated

morgan

commented

The product stack is called "Zynq 7000 Soc" (see https://www.amd.com/en/products/adaptive-socs-and-fpgas/soc/zynq-7000.html) The product stack is called "Zynq 7000 Soc" (see https://www.amd.com/en/products/adaptive-socs-and-fpgas/soc/zynq-7000.html)

|

||||

\item{SD card flash memory}

|

||||

\end{itemize}

|

||||

|

||||

\section{Applications}

|

||||

|

||||

\begin{itemize}

|

||||

\item{Run ARTIQ kernels}

|

||||

\item{Communicate with the host}

|

||||

\item{Control other Sinara EEM cards}

|

||||

\item{Distributed Real-Time I/O}

|

||||

\end{itemize}

|

||||

|

||||

\section{General Description}

|

||||

|

||||

The 1125 Kasli-SoC Carrier card is an 8hp EEM module, designed to run ARTIQ-Zynq kernels sent over the network from a host machine. Kasli-SoC is built around a Xilinx Zynq-7 SoC, allowing it to run more complex computations at high speed than its sister card 1124 Kasli 2.0. It supports up to 12 EEM connections to other EEM cards in the ARTIQ-Sinara family and up four SFP connections for comunications with other carriers. A dedicated Ethernet port is used for communications with the host.

|

||||

|

architeuthis marked this conversation as resolved

Outdated

morgan

commented

Zynq-7000 Zynq-7000

|

||||

|

||||

Real-time control of EEM daughtercards is implemented using the ARTIQ RTIO system. 1ns temporal resolution can be achieved for TTL events.

|

||||

|

||||

4 SFP 6Gb/s slots are provided. These can be used by the ARTIQ Distributed Real-Time Input/Output (DRTIO) system, which allows for the use of additional core devices (e.g. Kasli 2.0, Kasli-SoC) as satellite cards, capable of running subkernels or distributing commands from the \mbox{DRTIO} master.

|

||||

|

architeuthis marked this conversation as resolved

Outdated

mwojcik

commented

Kasli 1.0/1.1 is also supported. I'd put it as Kasli 1.0/1.1 is also supported.

I'd put it as ``e.g. Kasli or another Kasli-SoC`` (technically it's also compatible with kc705/zc706 but most users will not even see these boards)

mwojcik

commented

``distributing commands`` sounds a bit weird too

I assume that's for RTIO - that is, controlling the peripherals - and it's the primary function that should be put first.

and of course yes, it can distribute them (to further satellites) but it also adheres to the commands, but this time I don't know how to put it better

architeuthis

commented

The idea was distributing commands [to the peripherals] as opposed to controlling them directly. Better like so? The idea was distributing commands [to the peripherals] as opposed to controlling them directly. Better like so?

mwojcik

commented

'to the peripherals' clears it up nicely I think. 'to the peripherals' clears it up nicely I think.

|

||||

|

||||

% Switch to next column

|

||||

\vfill\break

|

||||

|

||||

% TODO, possibly: block diagram

|

||||

|

||||

\begin{figure}[hbt!]

|

||||

\centering

|

||||

\includegraphics[height=3in]{photo1125.jpg}

|

||||

\caption{Kasli-SoC card}

|

||||

\includegraphics[angle=90,height=1in]{Kasli-SoC_FP.pdf}

|

||||

\caption{Kasli-SoC front panel}

|

||||

\end{figure}

|

||||

|

||||

% END PAGE ONE (for wide pages a single-column layout is preferable)

|

||||

\onecolumn

|

||||

|

||||

\sourcesection{Kasli-SoC}{https://github.com/sinara-hw/Kasli-SOC/}

|

||||

|

||||

\section{Electrical Specifications}

|

||||

|

||||

% DATASHEET: https://docs.amd.com/v/u/en-US/ds190-Zynq-7000-Overview

|

||||

|

architeuthis marked this conversation as resolved

Outdated

mwojcik

commented

Looking at Kasli 2.0's specs, they're the same for Kasli-SoC. Looking at Kasli 2.0's specs, they're the same for Kasli-SoC.

morgan

commented

The kasli used the "DC and AC Switching Characteristics" instead of product overview datasheet, here's the Zynq-7000 version for that DS191 The kasli used the "DC and AC Switching Characteristics" instead of product overview datasheet, here's the Zynq-7000 version for that [DS191](https://docs.amd.com/v/u/en-US/ds191-XC7Z030-XC7Z045-data-sheet)

|

||||

|

||||

\textbf{TODO}

|

||||

|

||||

\begin{table}[h]

|

||||

\centering

|

||||

\begin{threeparttable}

|

||||

\caption{Recommended Operating Conditions}

|

||||

\begin{tabularx}{0.85\textwidth}{l | c c c | c | X}

|

||||

\thickhline

|

||||

\textbf{Parameter} & \textbf{Min.} & \textbf{Typ.} & \textbf{Max.} &

|

||||

\textbf{Unit} & \textbf{Conditions} \\

|

||||

\hline

|

||||

\thickhline

|

||||

\end{tabularx}

|

||||

\end{threeparttable}

|

||||

\end{table}

|

||||

|

||||

Power is to be supplied through the barrel connector in the front panel, size 5.5 mm OD, 2.5 mm ID, and is passed on to daughtercards through the EEM connections. Locking barrel connectors are supported.

|

||||

|

architeuthis marked this conversation as resolved

Outdated

mwojcik

commented

Alternatively, there's a Molex connector on the back of the card, to be used with the 1106 EEM AC Power Module. (also applies to Kasli 2.0) Alternatively, there's a Molex connector on the back of the card, to be used with the 1106 EEM AC Power Module. (also applies to Kasli 2.0)

|

||||

|

||||

\section{SoC}

|

||||

|

||||

Kasli-SoC features a XC7Z030 Xilinx Zynq-7000 System-on-Chip with a Kintex-7 FGPA and an Cortex-A9 dual-core processor to facilitate high-speed real-time control of inputs and outputs. The use of the SoC allows for more complex computations at higher speed than Kasli 2.0's purely on-FPGA CPU. Usually, the SoC is flashed with firmware and gateware binaries compiled from the ARTIQ (Advanced Real-Time Infrastructure for Quantum physics) control system, which equips the carrier board with the ability to control other Sinara EEMs and run ARTIQ experiment kernels.

|

||||

|

architeuthis marked this conversation as resolved

Outdated

morgan

commented

FYI the exact part number is XC7Z030-3FFG676E FYI the exact part number is XC7Z030-3FFG676E

|

||||

|

||||

A micro-USB located on the front panel is equipped for JTAG, I2C, and UART serial output. The serial interface runs at 115200bps 8-N-1.

|

||||

|

||||

\artiqsection

|

||||

|

||||

ARTIQ-supported core devices based on Zynq-7000 SoCs, including Kasli-SoC, require firmware and gateware compiled from the ARTIQ-Zynq port, which can be found in the repository \url{https://git.m-labs.hk/M-Labs/artiq-zynq}.

|

||||

|

||||

\noteondrtio{Kasli-SoC}

|

||||

|

||||

\section{Communication Interfaces}

|

||||

|

||||

Communication between core devices is implemented with 1000Base-T small form-factor pluggable (SFP) interfaces. Four are available on 1125 Kasli-SoC. Appropriate SFP transceivers must be plugged inside the corresponding SFP cages. Each SFP connector possesses an indicator LED.

|

||||

|

architeuthis marked this conversation as resolved

Outdated

morgan

commented

I don't think we support SFP -> RJ45 on soc, maybe I am wrong I don't think we support SFP -> RJ45 on soc, maybe I am wrong

mwojcik

commented

we don't we don't

|

||||

|

||||

Additionally, a RJ45 10/100/1000T Ethernet port is featured for network connection to a host machine.

|

||||

|

||||

\subsection{Upstream connection}

|

||||

|

||||

\begin{itemize}

|

||||

\item \textbf{Standalone/Master} \\

|

||||

A network-connected Ethernet cable should be attached the front panel Ethernet port to enable communication with a host machine.

|

||||

\item \textbf{Satellite} \\

|

||||

Satellites must acquire an upstream connection to another satellite or the master. The \texttt{SFP0} port should be connected to one of the free SFP slots on an upstream core device, using a cable connection with SFP transceivers.

|

||||

|

architeuthis marked this conversation as resolved

Outdated

mwojcik

commented

cable (direct attach cable) or fiber connection cable (direct attach cable) _or fiber_ connection

architeuthis

commented

Only for SoC or in both sheets? Only for SoC or in both sheets?

mwojcik

commented

both both

|

||||

\end{itemize}

|

||||

|

||||

\subsection{Downstream connection}

|

||||

Kasli-SoC supports up to 4 DRTIO satellite connections per device. Any of the 3 downstream SFP ports (i.e. \texttt{SFP1}, \texttt{SFP2}, \texttt{SFP3}) may be freely used. On a master device, \texttt{SFP0} can also be used for a downstream connection, though some care is required with the enusing DRTIO destination numbers.

|

||||

|

architeuthis marked this conversation as resolved

Outdated

mwojcik

commented

ensuring? Not much care by default, I'd say - default routing table goes dest 1 - sfp0, dest 2 - sfp1 etc.; ``though some care is required with the enusing DRTIO destination numbers.``

ensuring?

Not much care by default, I'd say - default routing table goes dest 1 - sfp0, dest 2 - sfp1 etc.;

architeuthis

commented

"ensuing". but nvm, I entirely misread what I thought I was referencing. "ensuing". but nvm, I entirely misread what I thought I was referencing.

|

||||

|

||||

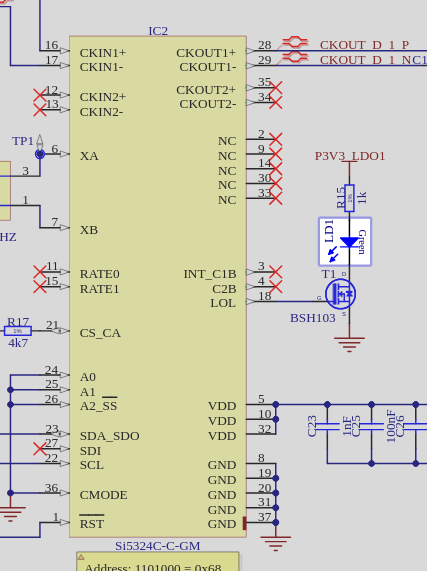

\clockingsection{Kasli-SoC}{SoC}

|

||||

|

||||

\section{Configuring Boot Mode}

|

||||

|

||||

Kasli-SoC is capable of booting either remotely, over JTAG USB, or directly from the SD card. See the ARTIQ manual for more instructions on how to correctly flash and boot a core device. Boot mode must be configured by flipping physical switches on the board. The boot mode DIP switches are located in the middle of the board. To boot from USB, flip both switches towards the label \texttt{JTAG}. To boot from the SD card, flip both switches towards the label \texttt{SD}.

|

||||

|

||||

\begin{figure}[hbt!]

|

||||

\centering

|

||||

\includegraphics[height=3in]{kasli-soc_dip_switches.jpg}

|

||||

\caption{Position of DIP switches, SD card, and POR pins}

|

||||

\end{figure}

|

||||

|

||||

\subsection{POR jumpers and POR reset}

|

||||

|

||||

A known Xilinx hardware bug prevents repeatedly booting over JTAG without a POR reset. If necessary, repeated boots can be made possible by physically setting a jumper on the POR pins (marked above) and triggering a reset over JTAG, see also the M-Labs POR reset script.\footnote{\url{https://git.m-labs.hk/M-Labs/zynq-rs/src/branch/master/kasli_soc_por.py}}

|

||||

|

||||

\section{User LEDs}

|

||||

|

||||

Kasli-SoC designates two user LEDs for debugging purposes. Both are located on the PCB. The first, labeled \texttt{USER0}, can be found at the very bottom left of the PCB, below the SFP cage. The second, labeled \texttt{LD1}, can be found at the top left, roughly behind the micro-USB port.

|

||||

|

architeuthis marked this conversation as resolved

Outdated

mwojcik

commented

is is ``LD1`` available for the kernels anyway?

architeuthis

commented

A second LED is. I'm not 100% that this is LD1 but I thought that's what I remembered it being. [_A_ second LED is](https://github.com/m-labs/migen/blob/c19ae9f8ae162ffe2d310a92bfce53ac2a821bc8/migen/build/platforms/sinara/kasli_soc.py#L7C27-L7C31). I'm not 100% that this is LD1 but I thought that's what I remembered it being.

mwojcik

commented

LD1 is a visual Loss of Lock indicator for Si5324: The second USER LED is visible on the front panel, below the Ethernet port. LD1 is a visual Loss of Lock indicator for Si5324:

The second USER LED is visible on the front panel, below the Ethernet port.

architeuthis

commented

Oops. Got it. (That isn't marked on the FP diagram used in the shop, though.) Oops. Got it. (That isn't marked on the FP diagram used in the shop, though.)

|

||||

|

||||

\sysdescsection

|

||||

|

||||

An example description file for a system using 1125 Kasli-SoC as a master core device might begin:

|

||||

|

||||

\begin{tcolorbox}[colback=white]

|

||||

\begin{minted}{json}

|

||||

"target": "kasli_soc",

|

||||

"variant": "my_variant",

|

||||

"hw_rev": "v1.0",

|

||||

"base": "master",

|

||||

"peripherals": [ ]

|

||||

\end{minted}

|

||||

\end{tcolorbox}

|

||||

|

||||

\coresysdesc

|

||||

|

||||

\newpage

|

||||

|

||||

\coredevicecode{1125 Kasli-SoC carrier}

|

||||

|

||||

\ordersection{1125 Carrier Kasli-SoC}

|

||||

|

||||

\finalfootnote

|

||||

|

||||

\end{document}

|

||||

2

Makefile

@ -1,4 +1,4 @@

|

||||

inputs = 1124 2118-2128 2238 2245 4410-4412 4456 5108 5432 5518-5528 5568 7210

|

||||

inputs = 1124 1125 2118-2128 2238 2245 4410-4412 4456 5108 5432 5518-5528 5568 7210

|

||||

dir = build

|

||||

|

||||

all: $(inputs)

|

||||

|

||||

BIN

images/1125/Kasli-SoC_FP.pdf

Normal file

BIN

images/1125/kasli-soc_dip_switches.jpg

Normal file

|

After Width: | Height: | Size: 204 KiB |

BIN

images/1125/photo1125.jpg

Normal file

|

After Width: | Height: | Size: 304 KiB |

The 6Gb/s bugs me even on the kasli datasheet, as the kasli fpga GTP transceiver max speed is around 6Gb/s but the DRTIO are running at 2.5Gb/s with 8b10b encoding. So if we are running this logic of using the max speed of the transceivers, the kasli-soc should be 12.5Gb/s. Though, I am not sure any SFP module support that kind of speed. (see https://www.amd.com/en/products/adaptive-socs-and-fpgas/technologies/high-speed-serial.html for the MGT linerate)

Is having both numbers (current revision) better?

Yes.

Also the CoaXpress adapter will use the SFPs at maximum speed on SoC.