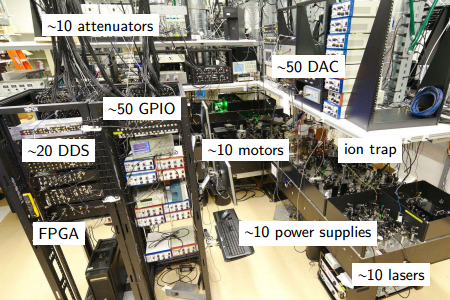

ARTIQ (Advanced Real-Time Infrastructure for Quantum physics) is a leading-edge control system for quantum information experiments. It was initiated and is supported by the Ion Storage Group at NIST, and its applicability reaches beyond ion trapping.

Modern research on quantum information systems poses particular challenges to the control system:

ARTIQ features a high-level programming language, based on Python, that helps describing complex experiments. It is compiled and executed on dedicated FPGA hardware with nanosecond timing resolution and sub-microsecond latency.

The time-critical code (a kernel) running on the FPGA (the core device) is easily interfaced with Python code on the computer using a remote procedure call (RPC) mechanism.

The FPGA design is highly portable so that it can adapt to different laboratory setups and resist hardware obsolescence.

ARTIQ drivers for non-realtime devices can be run on remote machines with different operating systems.

The project also includes a graphical user interface, an experiment scheduling system, and databases for experiments, devices, parameters and results.

Technologies employed include Python, Migen, MiSoC/mor1kx, LLVM and llvmlite.

Another goal of ARTIQ is to streamline and simplify the design flow of quantum physics instrumentation by promoting design reuse through the development of platform-independent, open-source hardware and software.

Our aim is to provide a control system suitable for the challenges of modern quantum information research, which is based on modular, parameterized and open components that allow physicists to rapidly design and deploy new experiments.

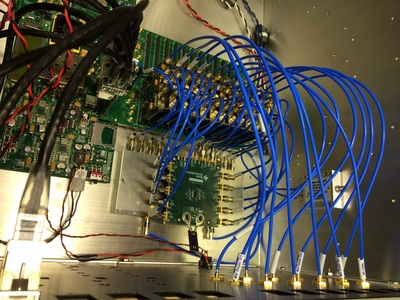

The ARTIQ core device currently uses hardware built in-house by physicists (based on a Xilinx KC705 development board with custom FMC cards). To improve the quality, features and scalability of ARTIQ systems, we are developing the Sinara device family. It aims at providing turnkey control hardware that is reproducible, open, flexible, modular, well-tested, and well-supported by the ARTIQ control software.

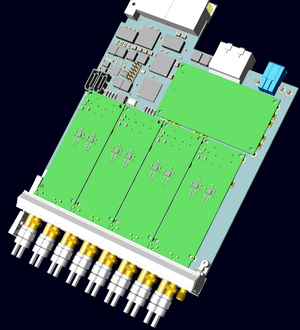

One of the main devices in the Sinara family is the Sayma card, which includes 8 channels of 2.4GSPS 16-bit DACs and a Kintex Ultrascale FPGA. The FPGA synthesizes waveforms for the DACs and our gateware supports two-tone direct digital synthesis and shaping of the waveform parameters with splines. Multiple Sayma cards can be installed in a MicroTCA chassis and synchronized.

The Sinara hardware is still in development, and more information is available on the wiki. Most of the hardware engineering is done at the Institute for Electronics Systems at the Warsaw University of Technology.

The core device is based on the resource-efficient MiSoC system-on-chip design, and you can use a limited version of ARTIQ with the small and low-cost Pipistrello board. See the manual for instructions. Note that Windows is not currently supported with the Pipistrello due to problems with the Windows PPP stack, so you will need a Linux system for trying ARTIQ on the Pipistrello. Feel free to send feedback to the mailing list, report problems to the GitHub issue tracker and submit pull requests!

ARTIQ was initiated by the Ion Storage Group at NIST, and several other institutions have later contributed to ARTIQ and/or Sinara.

|

|

|

|

|