# iCE40 I<sup>2</sup>C and SPI Hardened IP Usage Guide

# **Technical Note**

FPGA-TN-02010-1.7

August 2020

#### Disclaimers

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## **Contents**

| 1.       | Introduction                                                    |    |

|----------|-----------------------------------------------------------------|----|

| 2.       |                                                                 | -  |

| 2        | 2.1. Key Features for iCE40LM, iCE40 Ultra, and iCE40 UltraPlus | 6  |

| 2        | 2.2. Key Features for iCE40 Ultra Lite                          | 6  |

| 3.       | I <sup>2</sup> C Usage with Module Generation                   | 7  |

| 3        | 3.1. General Call Enable                                        | 8  |

| 3        | 3.2. Wakeup Enable                                              | 8  |

| 3        | 3.3. Master Clock (Desired)                                     | 8  |

| 3        | 3.4. Master Clock (Actual)                                      | 8  |

| 3        | 3.5. I <sup>2</sup> C Addressing                                | 8  |

|          | 3.5.1. FIFO Mode CLK Stretch Enable                             | 8  |

| 3        | 3.6. Interrupts                                                 | 8  |

|          | 3.6.1. Arbitration Lost Interrupts                              | 9  |

|          | 3.6.2. TX/RX Ready                                              | 9  |

|          | 3.6.3. Overrun or NACK                                          | 9  |

|          | 3.6.4. General Call Interrupts                                  | 9  |

| 3        | 3.7. FIFO Interrupts                                            | 9  |

|          | 3.7.1. General Call                                             | 9  |

|          | 3.7.2. Receive NACK                                             |    |

|          | 3.7.3. Mater Read Complete                                      |    |

|          | 3.7.4. Arbitration Lost Interrupts                              |    |

|          | 3.7.5. TX FIFO SYNC                                             |    |

|          | 3.7.6. TX FIFO Underflow                                        |    |

|          | 3.7.7. TX FIFO Overflow                                         | 10 |

| 3        | 3.8. Include I/O Buffers                                        |    |

| 4.       | SB_I2C Hard IP Macro Ports and Wrapper Connections              |    |

| 5.       | I <sup>2</sup> C Usage Cases                                    |    |

| 6.       | SPI IP Core Overview                                            |    |

| . 6      | 5.1. Key Features                                               |    |

| 7.       |                                                                 |    |

|          | 7.1. SPI Mode (Enable Slave Interface)                          |    |

|          | 7.2. SPI Mode (Enable Master Interface)                         |    |

|          | 7.3. Master Clock Rate (Desired)                                |    |

|          | 7.4. Master Clock Rate (Actual)                                 |    |

|          | 7.5. LSB First                                                  |    |

|          | 7.6. Inverted Clock                                             |    |

|          | 7.7. Phase Adjust                                               |    |

|          | 7.8. Slave Handshake Mode                                       |    |

|          | 7.9. Master Chip Selects                                        |    |

|          | 7.10. SPI Controller Interrupts                                 |    |

|          | 7.10.1. TX Ready                                                |    |

|          | 7.10.2. RX Ready                                                |    |

|          | 7.10.3. TX Overrun                                              |    |

|          | 7.10.4. RX Overrun                                              |    |

| -        | 7.11. Wakeup Enable                                             |    |

| -        | 7.12. Include I/O Buffers                                       |    |

| 8.       | SB_SPI Hard IP Macro Ports and Wrapper Connections              |    |

| 8.<br>9. | iCE40LM, iCE40 Ultra, and iCE40 UltraPlus SPI Usage Cases       |    |

| -        | Module Generator                                                |    |

|          | 10.1. Key Features                                              |    |

| -        | 10.1.1. Enable Left I <sup>2</sup> C                            |    |

|          | 10.1.1. Enable Efft C                                           |    |

|          |                                                                 |    |

| 10.1.3. Enable Left SPI            | 23 |

|------------------------------------|----|

| 10.1.4. Enable Right SPI           | 23 |

| 10.1.5. System Clock               |    |

| 10.1.6. Configuration Clock Source |    |

| Technical Support Assistance       |    |

| Revision History                   |    |

## Figures

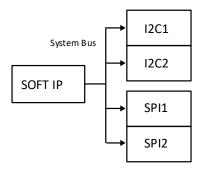

| Figure 1.1. IP Block Diagram for iCE40LM, iCE40 Ultra, and ICE40 UltraPlus                                        | 5  |

|-------------------------------------------------------------------------------------------------------------------|----|

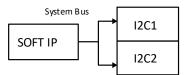

| Figure 1.2. IP Block Diagram for iCE40 UltraLite                                                                  | 5  |

| Figure 3.1. I <sup>2</sup> C Module GUI for iCE40LM, iCE40 Ultra, and iCE40 UltraPlus                             |    |

| Figure 3.2. I <sup>2</sup> C Module GUI for iCE40 UltraLite                                                       |    |

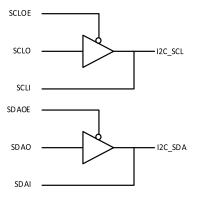

| Figure 3.3. I <sup>2</sup> C I/O Buffers                                                                          | 10 |

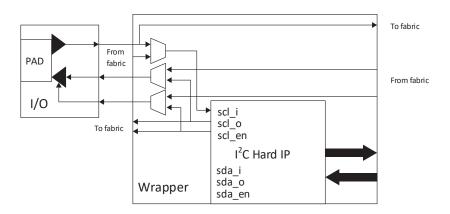

| Figure 3.4. I <sup>2</sup> C I/O Connections                                                                      | 10 |

| Figure 5.1. I <sup>2</sup> C Circuit                                                                              | 13 |

| Figure 7.1. SPI Module GUI for iCE40LM, iCE40 Ultra, and iCE40 UltraPlus                                          |    |

| Figure 7.2. SPI I/O Buffers included                                                                              | 17 |

| Figure 7.3. SPI I/O Buffers included                                                                              | 18 |

| Figure 9.1. External Master SPI Device Accessing the Slave User SPI                                               | 20 |

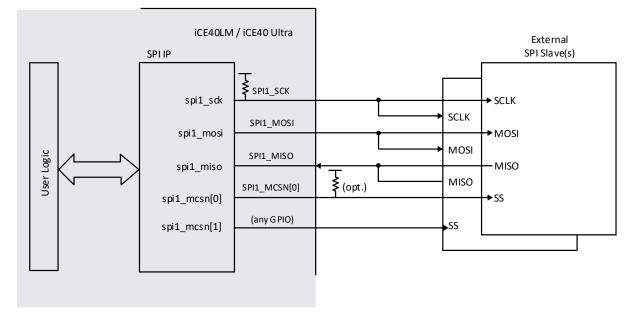

| Figure 9.2. iCE40LM, iCE40 Ultra and iCE40 UltraPlus User SPI Master Accessing One or Multiple External Slave SPI |    |

| Devices                                                                                                           | 21 |

| Figure 10.1. Soft IP Block Diagram                                                                                | 22 |

| Figure 10.2. Module Generator                                                                                     | 23 |

## Tables

| Table 4.1. Pins for the Hard I <sup>2</sup> C IP for iCE40LM, iCE40 Ultra, and iCE40 UltraPlus | 11 |

|------------------------------------------------------------------------------------------------|----|

| Table 4.2. Pins for the Hard I <sup>2</sup> C IP for iCE40 UltraLite                           |    |

| Table 8.1. Pins for the Hard SPI IP                                                            |    |

## 1. Introduction

The iCE40<sup>™</sup> family of devices is an ultra-low power FPGA and sensor manager designed for ultra-low power mobile applications, such as smartphones, tablets and hand-held devices. The iCE40LM, iCE40 Ultra<sup>™</sup> and iCE40 UltraPlus<sup>™</sup> include integrated SPI and I<sup>2</sup>C blocks, while the iCE40 UltraLite<sup>™</sup> includes an I<sup>2</sup>C block only, to interface with virtually all mobile sensors and application processors.

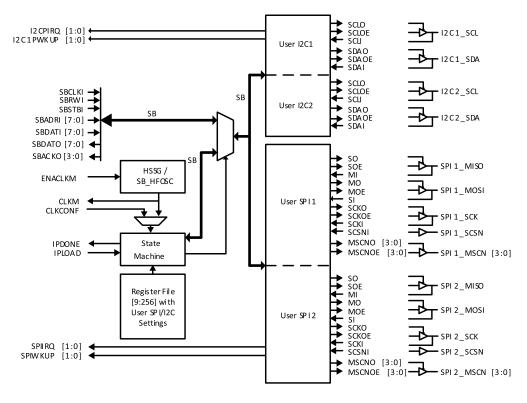

The key components available for iCE40LM, iCE40 Ultra and iCE40 UltraPlus:

- Two I<sup>2</sup>C IP cores located at the upper left corner and upper right corner of the chip

- Two SPI IP cores located at lower left corner and lower right corner of the chip

The key components available for iCE40 UltraLite:

• Two I<sup>2</sup>C IP cores located at the lower left corner and lower right corner of the chip

Each device uses a System Bus to connect its Hard IP to the fabric. The device does not preload the Hard IP registers during configuration, thus, a soft IP is required. Using Module Generator to generate the IP is recommended because Module Generator generates the corresponding soft IP as well. For details, refer to Module Generator section.

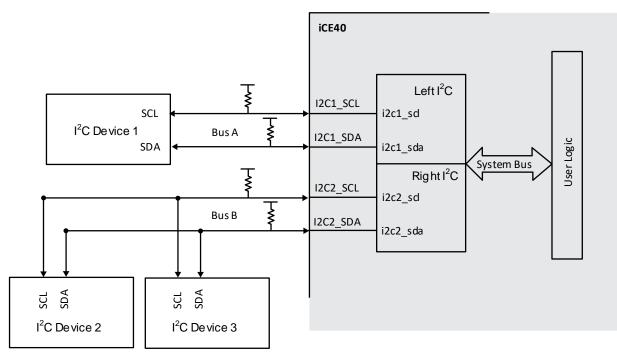

Figure 1.1. IP Block Diagram for iCE40LM, iCE40 Ultra, and ICE40 UltraPlus

Figure 1.2. IP Block Diagram for iCE40 UltraLite

## 2. I<sup>2</sup>C IP Core Overview

The I<sup>2</sup>C hard IP provides industry standard two pin communication interface that conforms to V2.1 of the I<sup>2</sup>C bus specification. It could be configured as either master or slave port. In master mode, it supports configurable data transfer rate and performs arbitration detection to allow it to operate in multi-master systems. It supports clock stretching in both master and slave modes with enable/disable capability. It supports both 7 bits and 10 bits addressing in slave mode with configurable slave address. It supports general call address detection in both master and slave mode. It provides interrupt logic for easy communicating with host. It also provides configurable digital delay at SDA output for reliably generating start/stop condition.

### 2.1. Key Features for iCE40LM, iCE40 Ultra, and iCE40 UltraPlus

- Configurable Master and Slave mode

- Support for 7-bit or 10-bit configurable Slave Address

- Multi-master Arbitration support

- Clock stretching to ensure data setup time

- Up to 400 kHz Data Transfer Speed; also support 100 kHz, 50 kHz modes

- General Call Support

- Master clock source from System Bus clock

- Communication with custom logic through 8-bit wide data bus

- Programmable 5 MSB bits for 7 bits Slave Address or 8 MSB bits for 10 bits Slave Address for user logic Slave I<sup>2</sup>C port.

- I<sup>2</sup>C port and all System Bus addressable registers are reset upon Power On Reset (POR)

- 30 ns analog delay required at SDA input for reliable START, STOP condition detection

- Interface to customer logic through the System Bus Interface

### 2.2. Key Features for iCE40 Ultra Lite

- Configurable Master and Slave mode

- Support for 7-bit or 10-bit configurable Slave Address

- Multi-master Arbitration support

- Clock stretching to ensure data setup time

- Up to 1000 kHz Data Transfer Speed, also supports 400 kHz, 100 kHz, 50 kHz modes

- General Call Support

- Optional delaying input or output data, or both

- Optional FIFO mode

- Transmit FIFO size is 10 bits x 16 bytes, receive FIFO size is 10 bits x 32 bytes

**#LATTICE**

## 3. I<sup>2</sup>C Usage with Module Generation

The Module generator is the recommended flow for using the I<sup>2</sup>C Hard IP block. Please see the Module Generator section for more information.

When the I<sup>2</sup>C portion of the Hard IP block is disabled, all settings on the I<sup>2</sup>C tab shall be disabled.

| Configuration Generator | Hard IP Enables I2C SPI<br>Left I2C<br>General<br>General call enable<br>Wakeup enable<br>Vakeup enable<br>Vinclude IO buffers<br>Master Clock Rate<br>Desired 100 V KHz<br>Actual KHz<br>I2C Addressing<br>7-Bit Addressing<br>10000 01 | Right IZC<br>General<br>General call enable<br>Wakeup enable<br>Vakeup enable<br>Include IO buffers<br>Master Clock Rate<br>Desired 100 V KHz<br>Actual KHz<br>IZC Addressing<br>7-Bit Addressing V |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI SPI                 | Interrupts Arbitration lost Tx/Rx ready Overrun or NACK General call                                                                                                                                                                     | Interrupts Arbitration lost Tx/Rx ready Overrun or NACK General call                                                                                                                                |

Figure 3.1. I<sup>2</sup>C Module GUI for iCE40LM, iCE40 Ultra, and iCE40 UltraPlus

| nfiguration Gener | ate Log |                                                                                                                                                                                                                                                                           | Configuration Gene | erate Log                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IzC IzC           | he Log  | Night IZC<br>System Bus Interrupts<br>System Bus Interrupts<br>Ty/RxReady<br>Overrun or NACK<br>General Call<br>FIFO Interrupts<br>General Call<br>Receive NACK<br>Master Read Complete<br>Arbitration Loat<br>T X: FIFO Sync<br>T X: FIFO Underflow<br>Rx: FIFO Overflow | IzC IzC            | rote Log Herd JP Enables I2C Inter Left I2C General General call enable Volkeup enable Include I20 buffers Master Clock Rate Desired 100 KHz I2C Addressing Z-B4 Addressing FIF0 FIF0 FIF0 FIF0 Enable FIF0 Mode CLK Stretch Enable RFFD Almost Full III IIIIIIIIIIIIIIIIIIIIIIIIIIIIIII | ups<br>Right IZC<br>General call enable<br>Woksup enable<br>Winclude ID buffers<br>Master Clock Rate<br>Desired 100 • KHz<br>Actual 10 |

|                   |         |                                                                                                                                                                                                                                                                           |                    |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Figure 3.2. I<sup>2</sup>C Module GUI for iCE40 UltraLite

### 3.1. General Call Enable

This setting enables the I<sup>2</sup>C General Call response (addresses all devices on the bus using the I<sup>2</sup>C address 0) in Slave mode. This setting can be modified dynamically by enabling the GCEN bit in the I<sup>2</sup>C Control Register I2CCR1.

### 3.2. Wakeup Enable

Turns on the I<sup>2</sup>C wakeup on address match. Enables the Wakeup port. The WKUPEN bit in the I2CCR1 can be modified dynamically allowing the Wake Up function to be enabled or disabled.

### 3.3. Master Clock (Desired)

This edit box allows the user to specify a desired master clock frequency. A calculation is then made to determine a divider value to generate a clock close to this value from the input clock. The frequency of the input System Bus clock is specified on the main/general tab. The divider value is rounded to the nearest integer after dividing the input System Bus clock by the value entered in this field.

### 3.4. Master Clock (Actual)

Since it is not always possible to divide the input System Bus clock to the exact value requested by the user, the actual value will be returned in this read-only field. When both the desired I<sup>2</sup>C clock and System Bus clock fields contain valid data and either is updated, the Master Clock field returns the value (FREQ\_SB / L2C\_CLK\_DIVIDER), rounded to an integer as shown in the example below. FREQ\_SB is the System Bus Clock Frequency customer will enter in the Module Generator. I2C\_CLK\_DIVIDER will be a factor to be calculated as in the example below.

Master Clock Calculation Example:

- 1. Divider = I2C\_CLK\_DIVIDER = FREQ\_SB / I2C\_CLK\_FREQ

- 2. Master Clock (Actual) = FREQ\_SB / DividerInteger

For example: FREQ\_SB = 42.5 MHz, I2C\_BUS\_PERF = 400 KHZ

1. Divider = I2C\_CLK\_DIVIDER = FREQ\_SB / I2C\_BUS\_PERF

Divider = 42500 / 400 = 106.25

Therefore ROUND DividerInteger = 106

2. Master Clock (Actual) = FREQ\_SB / DividerInteger

Actual frequency = 42500 / 106 = 400.9 kHz

In this example, if the user sees that an I2C\_CLK\_FREQ of 400 kHz cannot be generated, the user may choose to use the actual value or change the System Bus Clock. For this reason, the user needs to enter a frequency and the actual frequency will be displayed. This value may then be adjusted it desired.

### 3.5. I<sup>2</sup>C Addressing

This option allows the user to set 7-bit or 10-bit addressing and define the Hard I<sup>2</sup>C address.

### 3.5.1. FIFO Mode CLK Stretch Enable

Used in FIFO mode only. To ensure data setup time. If disabled, then overflow and underflow error flag must be monitored.

### 3.6. Interrupts

When any of the interrupts are enabled, the  $I^2C$  port is also enabled.

### **3.6.1.** Arbitration Lost Interrupts

An interrupt which indicates I<sup>2</sup>C lost arbitration. This interrupt is bit IRQARBL of the register I2CIRQ. When enabled, it indicates that ARBL is asserted. Writing a '1' to this bit clears the interrupt. This option can be changed dynamically by modifying the bit IRQARBLEN in the register I2CIRQEN.

#### 3.6.2. TX/RX Ready

An interrupt which indicates that the I<sup>2</sup>C transmit data register (I2CTXDR) is empty or that the receive data register (I2CRXDR) is full. The interrupt bit is IRQTRRDY of the register I2CIRQ. When enabled, it indicates that TRRDY is asserted. Writing a '1' to this bit clears the interrupt. This option can be changed dynamically by modifying the bit IRQTRRDYEN in the register I2CIRQEN.

#### 3.6.3. Overrun or NACK

An interrupt which indicates that the I2CRXDR received new data before the previous data. The interrupt is bit IRQROE of the register I2CIRQ. When enabled, it indicates that ROE is asserted. Writing a '1' to this bit clears the interrupt. This option can be changed dynamically by modifying the bit IRQROEEN in the register I2CIRQEN.

#### 3.6.4. General Call Interrupts

An interrupt which indicates that a general call has occurred. The interrupt is bit IRQHGC of the register I2CIRQ. When enabled, it indicates that ROE is asserted. Writing a '1' to this bit clears the interrupt. This option can be changed dynamically by modifying the bit IRQHGCEN in the register I2CIRQEN.

### 3.7. FIFO Interrupts

#### 3.7.1. General Call

An interrupt which indicates that a general call has occurred. The interrupt is bit IRQHGC of I2CFIFOIRQ. This bit can be changed by modifying the bit IRQHGCEN in the register I2CFIFOIRQEN.

#### 3.7.2. Receive NACK

An interrupt which indicates that a NACK has received. This is bit IRQRNACK of register I2CFIFOIRQ. This bit can be changed by modifying the bit IRQRNACKEN in register I2CFIFOIRQEN.

### 3.7.3. Mater Read Complete

A transaction is considered complete when 1) the specified number of data bytes from the slave have been received in the RX FIFO; or 2) the Master terminates the read transaction before the specified number of data bytes received. This is bit IRQMRDCMPL of register I2CFIFOIRQ. This bit can be changed by modifying the bit IRQMRDCMPLEN in register I2CFIFOIRQEN.

#### 3.7.4. Arbitration Lost Interrupts

An interrupt which indicates I<sup>2</sup>C lost arbitration. This interrupt is bit IRQARBL of the register I2CFIFOIRQ. When enabled, it indicates that ARBL is asserted. Writing a 1 to this bit clears the interrupt. This option can be changed dynamically by modifying the bit IRQARBLEN in the register I2CFIFOIRQEN.

#### 3.7.5. TX FIFO SYNC

An interrupt which indicates I<sup>2</sup>C TXFIFO Synchronization Error. Synchronization error happens when there are back-toback commands in the FIFO. The previous command is overwritten. This interrupt is bit IRQTXSERR of register I2CFIFOIRQ. This option can be changed dynamically by modifying the bit IRQRXSERREN in the register I2CFIFOIRQEN.

### 3.7.6. TX FIFO Underflow

FIFO TX underflow interrupt. mutually exclusive with clock stretching function. This interrupt is bit IRQTXUNDERF of register I2CFIFOIRQ. This option can be changed dynamically by modifying the bit IRQTXUNDERFEN in the register I2CFIFOIRQEN.

### 3.7.7. TX FIFO Overflow

FIFO RX overflow interrupt. mutually exclusive with clock stretching function. This interrupt is bit IRQRXOVERF of register I2CFIFOIRQ. This option can be changed dynamically by modifying the bit IRQRXOVERFEN in the register I2CFIFOIRQEN.

### 3.8. Include I/O Buffers

Includes buffers for the I<sup>2</sup>C pins.

Figure 3.3. I<sup>2</sup>C I/O Buffers

Figure 3.4. I<sup>2</sup>C I/O Connections

## 4. SB\_I2C Hard IP Macro Ports and Wrapper Connections

When the I<sup>2</sup>C Hard IP is enabled, the necessary signals are included in the generated module.

| Pin Name    | Pin Direction  | Description                                                                                                                                                                                                                                              |

|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBCLKi      | I              | System clock input                                                                                                                                                                                                                                       |

| SBWRi       | I              | System Read/Write input. R=0, W=1                                                                                                                                                                                                                        |

| SBSTBi      | I              | System Strobe Signal                                                                                                                                                                                                                                     |

| SBADRi[7:0] | I              | System Bus Control Registers Address                                                                                                                                                                                                                     |

| SBDATi[7:0] | I              | System Data Input                                                                                                                                                                                                                                        |

| SBDATo[7:0] | 0              | System Data Output                                                                                                                                                                                                                                       |

| SBACKo      | 0              | System Acknowledgement                                                                                                                                                                                                                                   |

| I2CPIRQ     | 0              | Interrupt request output signal of the I <sup>2</sup> C core – The intended use of this signal is for it to be connected to a Master controller (such as a microcontroller or state machine) and request an interrupt when a specific condition is met.  |

| I2CPWKUP    | 0              | Wake-up signal – The signal is enabled only if the Wakeup Enable feature is set.                                                                                                                                                                         |

| I2Cx_SCL*   | Bi-directional | Open drain clock line of the I <sup>2</sup> C core – The signal is an output if the I <sup>2</sup> C core is performing a Master operation. The signal is an input for Slave operations. This signal can use a dedicated I/O pin.                        |

| I2Cx_SDA1   | Bi-directional | Open drain data line of the I <sup>2</sup> C core – The signal is an output when data is transmitted from the I <sup>2</sup> C core. The signal is an input when data is received into the I <sup>2</sup> C core. This signal can use dedicated I/O pin. |

#### Table 4.1. Pins for the Hard I<sup>2</sup>C IP for iCE40LM, iCE40 Ultra, and iCE40 UltraPlus

\*Note: x indicates the  $I^2C$ : x=1 for the left  $I^2C$ ; x=2 for the right  $I^2C$ .

#### Table 4.2. Pins for the Hard I<sup>2</sup>C IP for iCE40 UltraLite

| Pin Name    | Pin Direction  | Description                                                                                                                                                                                                                                                                                           |

|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBCSi       | I              | This chip select signal activates the IP to allow system bus or fabric interface to communicate with the IP.                                                                                                                                                                                          |

| SBCLKi      | I              | System clock input                                                                                                                                                                                                                                                                                    |

| SBWRi       | I              | System Read/Write input. R=0, W=1                                                                                                                                                                                                                                                                     |

| SBSTBi      | I              | System Strobe Signal. When asserted, indicates that the slave component is selected.                                                                                                                                                                                                                  |

| SBADRi[3:0] | I              | System Bus Control Registers Address                                                                                                                                                                                                                                                                  |

| SBDATi[9:0] | I              | System Data Input [7:0] for register mode; [9:0] for FIFO mode                                                                                                                                                                                                                                        |

| SBDATo[9:0] | 0              | System Data Output [7:0] for register mode; [9:0] for FIFO mode                                                                                                                                                                                                                                       |

| SBACKo      | 0              | System Acknowledgement                                                                                                                                                                                                                                                                                |

| SBSRWo      | 0              | Slave read/write signal. A "1" indicates a slave transmitting (external master receiving). A "0" means slave receiving (external master transmitting).                                                                                                                                                |

| I2CPIRQ     | 0              | Interrupt request output signal of the I <sup>2</sup> C core – The intended use of this signal is for it to be connected to a Master controller (such as a microcontroller or state machine) and request an interrupt when a specific condition is met.                                               |

| I2CPWKUP    | 0              | Wake-up signal – The signal is enabled only if the Wakeup Enable feature is set.                                                                                                                                                                                                                      |

| FIFO_RST    | I              | Reset for the FIFO logic                                                                                                                                                                                                                                                                              |

| TXFIFO_AE   | 0              | TXFIFO almost empty status signal coming from TXFIFO, indicating user-defined almost empty threshold value is reached.                                                                                                                                                                                |

| TXFIFO_E    | 0              | TXFIFO empty signal coming from TXFIFO                                                                                                                                                                                                                                                                |

| TXFIFO_F    | 0              | TXFIFO full signal                                                                                                                                                                                                                                                                                    |

| RXFIFO_E    | 0              | RXFIFO is empty. It can be served as an active low DATA RDY signal.                                                                                                                                                                                                                                   |

| RXFIFO_AF   | 0              | RXFIFO almost full signal, indicating user-defined almost full threshold value is reached.                                                                                                                                                                                                            |

| RXFIFO_F    | 0              | RXFIFO full signal                                                                                                                                                                                                                                                                                    |

| MRDCMPL     | 0              | Master Read Complete – This is only valid for Master Read Mode.A transaction is considered complete when 1) the specified number of data bytes from the slave have been received in the RX FIFO; or 2) the Master terminates the read transaction before the specified number of data bytes received. |

| I2Cx_SCL*   | Bi-directional | Open drain clock line of the I <sup>2</sup> C core – The signal is an output if the I <sup>2</sup> C core is performing a Master operation. The signal is an input for Slave operations. This signal can use a dedicated I/O pin.                                                                     |

| I2Cx_SDA*   | Bi-directional | Open drain data line of the $I^2C$ core – The signal is an output when data is transmitted from the $I^2C$ core. The signal is an input when data is received into the $I^2C$ core. This signal can use dedicated I/O pin.                                                                            |

**\*Note:** x indicates the  $I^2C$ : x=1 for the left  $I^2C$ ; x=2 for the right  $I^2C$ .

## 5. I<sup>2</sup>C Usage Cases

The I<sup>2</sup>C usage cases described below refer to Figure 5.1.

- 1. Master iCE40 I<sup>2</sup>C Accessing Slave External I<sup>2</sup>C Devices

- a. A System Bus Master is implemented in the iCE40 logic.

- b. I<sup>2</sup>C devices 1, 2, and 3 are all Slave devices.

- c. The Master performs bus transactions to the left I<sup>2</sup>C controller to access external Slave I<sup>2</sup>C Device 1 on Bus A.

- d. The Master performs bus transactions to the right I<sup>2</sup>C controller to access the external Slave I<sup>2</sup>C Devices number 2 or 3 on Bus B.

- 2. External Master I<sup>2</sup>C Device Accessing Slave iCE40 I<sup>2</sup>C

- a. The  $I^2C$  devices 1, 2, and 3 are  $I^2C$  Master devices.

- b. The external master I<sup>2</sup>C Device 1 on Bus A performs I<sup>2</sup>C memory cycles to access the left I<sup>2</sup>C controller using address yyyxxxxx01.

- c. The external master I<sup>2</sup>C Device 2 or 3 on Bus B performs I<sup>2</sup>C memory cycles to access the right I<sup>2</sup>C User with the address yyyxxxx10.

- d. A Master in the iCE40 fabric must manage data reception and transmission. The Master can use interrupts or polling techniques to manage data transfer, and to prevent data overrun conditions.

Figure 5.1. I<sup>2</sup>C Circuit

## 6. SPI IP Core Overview

The SPI hard IP provide industry standard four-pin communication interface with 8 bit wide System Bus to communicate with System Host. It could be configured as Master or Slave SPI port with separate Chip Select Pin. In master mode, it provides programmable baud rate, and supports CS HOLD capability for multiple transfers. It provides variety status flags, such as Mode Fault Error flag, Transmit/Receive status flag etc. for easy communicate with system host.

### 6.1. Key Features

Configurable Master and slave mode

- Full-Duplex data transfer

- Mode fault error flag with CPU interrupt capability

- Double-buffered data register

- Serial clock with programmable polarity and phase

- LSB First or MSB First Data Transfer

- Communicate with custom logic through 8 bit wide System Bus

- Maximum 4 Slave select output could be routed to any I/O through fabric for Master mode

- Slave chip select pin could be routed to any I/O through fabric for custom logic

- Clock source for Master clock (MCLK) generation come from System Bus clock

- Optionally send out status byte to inform remote SPI master the slave receiving register status during slave write.

- Optionally enable the Slow Response Mode for slave SPI read, which will automatically deploy the Lattice specific protocol to resolve the issue that caused by the slow initial respond of the System host at high SPI clock rate.

- The SPI port and all System Bus addressable registers will be reset upon Power On Reset (POR)

- Interface to customer logic through the System Bus Interface

**#LATTICE**

## 7. SPI Usage with Module Generation

The Module generator is the recommended flow for using the SPI Hard IP block. See the Module Generator section for more information.

When the SPI portion of the Hard IP block is disabled, all settings on the SPI tab shall be disabled.

| I2C I2C | Hard IP Enables I2C SPI<br>Left SPI<br>I Enable slave interface<br>Enable master interface<br>Master Clock Rate<br>Desired 1 MHz<br>Actual MHz<br>Master Chip Selects                       | Right SPI<br>Finable slave interface<br>Enable master interface<br>Master Clock Rate<br>Desired 1 MHz<br>Actual MHz<br>Master Chip Selects<br>1  Interrupts |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI SPI | Interrupts<br>T x ready<br>X voerrun<br>R x ready<br>R x overrun<br>General<br>Wakeup enable<br>LSB first<br>Phase adjust<br>Inverted clock<br>Slave handshake mode<br>V Include IO buffers | Interrupts Tx ready Tx overrun Rx ready Rx overrun General Wakeup enable LSB first Phase adjust Inverted clock Slave handshake mode I Include IO buffers    |

Figure 7.1. SPI Module GUI for iCE40LM, iCE40 Ultra, and iCE40 UltraPlus

### 7.1. SPI Mode (Enable Slave Interface)

This option allows the user to enable Slave Mode interface for the initial state of the SPI block. By default, Slave Mode interface is enabled. Options and ports that are applicable to only one mode will be disabled when the other is chosen.

### 7.2. SPI Mode (Enable Master Interface)

This option allows the user to enable Master Mode interface for the initial state of the SPI block. This option can be updated dynamically by modifying the MSTR bit of the register SPICR2. Options and ports that are applicable to only one mode will be disabled when the other is chosen.

### 7.3. Master Clock Rate (Desired)

("Enable Master Interface" only) This edit box allows the user to specify a desired master clock frequency. A calculation is then made to determine a divider value to generate a clock close to this value from the input clock. The frequency of the input System Bus clock is specified on the main/general tab. The divider value is rounded to the nearest integer after dividing the input System Bus clock by the value entered in this field.

### 7.4. Master Clock Rate (Actual)

("Enable Master Interface" only) Since it is not always possible to divide the input System Bus clock exactly to that requested by the user, the actual value will be returned in this read-only field. When both the desired SPI clock and System Bus clock fields have valid data and either is updated, this field returns the value (FREQ\_SB/SPI\_CLK\_DIVIDER), rounded to two decimal places as shown in the example below. FREQ\_SB is the System Bus Clock Frequency that the customer enters in the Module Generator. SPI\_CLK\_DIVIDER is a factor to be calculated, which is also shown in the example below.

Master Clock Calculation Example:

- 1. Divider = SPI\_CLK\_DIVIDER = FREQ\_SB / SPI\_CLK\_FREQ

- 2. Master Clock (Actual) = FREQ\_SB / DividerInteger

For example: FREQ\_SB = 66 MHz, SPI\_CLK\_FREQ = 25 MHZ

- Divider = SPI\_CLK\_DIVIDER = FREQ\_SB / SPI\_CLK\_FREQ Divider = 66 / 25 = 2.64 Therefore ROUND DividerInteger = 3

- 2. Master Clock (Actual) = FREQ\_SB / DividerInteger

```

Actual frequency = 66 / 3 = 22 MHz

```

In this example, if the user sees that an SPI\_CLK\_FREQ of 25 MHz cannot be generated, the user may choose to use the actual value or change the System Bus Clock. For this reason, the user needs to enter a frequency and the actual frequency will be displayed. This value may then be adjusted it desired.

### 7.5. LSB First

This setting specifies the order of the serial shift of a byte of data. The data order (MSB or LSB first) is programmable within the SPI core. This option can be updated dynamically by modifying the LSBF bit in the register SPICR2.

### 7.6. Inverted Clock

The inverts the clock polarity used to sample and output data is programmable for the SPI core. When selected the edge changes from the rising to the falling clock edge. This option can be updated dynamically by accessing the CPOL bit of register SPICR2.

### 7.7. Phase Adjust

An alternate clock-data relationship is available for SPI devices with particular requirements. This option allows the user to specify a phase change to match the application. This option can be updated dynamically by accessing the CPHA bit in the register SPICR2.

### 7.8. Slave Handshake Mode

Enables Lattice proprietary extension to the SPI protocol. For use when the internal sup-port circuit (e.g. WISHBONE host) cannot respond with initial data within the time required, and to make the Slave read out data predictably available at high SPI clock rates. This option can be updated dynamically by accessing the SDBRE bit in the register SPICR2.

### 7.9. Master Chip Selects

("Enable Master Interface" only) The core has the ability to provide up to 4 individual chip select outputs for master operation. This field allows the user to prevent extra chip selects from being brought out of the core. This option can be updated dynamically by modifying the register SPICSR.

### 7.10. SPI Controller Interrupts

#### 7.10.1. TX Ready

An interrupt which indicates the SPI transmit data register (SPITXDR) is empty. The interrupt bit is IRQTRDY of the register SPIIRQ. When enabled, indicates TRDY was asserted. Write a '1' to this bit to clear the interrupt. This option can be change dynamically by modifying the bit IRQTRDYEN in the register SPIIRQEN.

#### 7.10.2. RX Ready

An interrupt which indicates the receive data register (SPIRXDR) contains valid receive data. The interrupt is bit IRQRRDY of the register SPIIRQ. When enabled, indicates RRDY was asserted. Write a '1' to this bit to clear the interrupt. This option can be change dynamically by modifying the bit IRQRRDYEN in the register SPICSR.

#### 7.10.3. TX Overrun

An interrupt which indicates the Slave SPI chip select (SPI\_SCSN) was driven low while a SPI Master. The interrupt is bit IRQMDF of the register SPIIRQ. When enabled, indicates MDF (Mode Fault) was asserted. Write a '1' to this bit to clear the interrupt. This option can be change dynamically by modifying the bit IRQMDFEN in the register SPIIRQEN.

#### 7.10.4. RX Overrun

An interrupt which indicates SPIRXDR received new data before the previous data. The interrupt is bit IRQROE of the register SPIIRQ. When enabled, indicates ROE was asserted. Write a '1' to this bit to clear the interrupt. This option can be change dynamically by modifying the bit IRQROEEN in the register SPIIRQEN.

### 7.11.Wakeup Enable

The core can optionally provide a wakeup signal to the device to resume from low power mode. This option can be updated dynamically by modifying the bit WKUPEN\_USER in the register SPICR1.

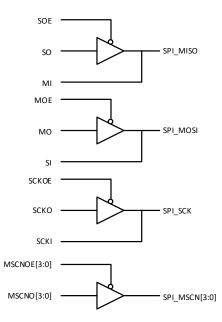

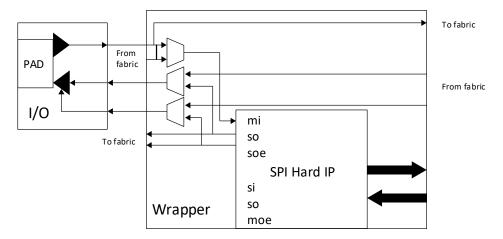

### 7.12.Include I/O Buffers

Includes buffers for the SPI pins.

Figure 7.2. SPI I/O Buffers included

Figure 7.3. SPI I/O Buffers included

## 8. SB\_SPI Hard IP Macro Ports and Wrapper Connections

When the SPI Hard IP is enabled, the necessary signals will be included in the generated module.

| Pin Name       | Pin<br>Direction   | Description                                                                                                                                                                                                                                                          |

|----------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBCLKi         | I                  | System clock input                                                                                                                                                                                                                                                   |

| SBWRi          | 0                  | System Read/Write input. R=0, W=1                                                                                                                                                                                                                                    |

| SBSTBi         | 0                  | System Strobe Signal                                                                                                                                                                                                                                                 |

| SBADRi[7:0]    | I                  | System Bus Control Registers Address                                                                                                                                                                                                                                 |

| SBDATi[7:0]    | I                  | System Data Input                                                                                                                                                                                                                                                    |

| SBDATo[7:0]    | 0                  | System Data Output                                                                                                                                                                                                                                                   |

| SBACKo         | 0                  | System Acknowledgement                                                                                                                                                                                                                                               |

| SPIPIRQ        | О                  | Interrupt request output signal of the I <sup>2</sup> C core – The intended use of this signal is for it to be connected to a Master controller (i.e. a microcontroller or state machine) and request an interrupt when a specific condition is met.                 |

| SPIPWKUP       | 0                  | Wake-up signal – The signal is enabled only if the Wakeup Enable feature has been set.                                                                                                                                                                               |

| SPx_SCK*       | Bi-<br>directional | The signal is an output if the SPI core is in Master mode (MCLK). The signal is an input if the SPI core is in Slave mode (CCLK). This signal could use dedicated I/O pin.                                                                                           |

| SPx_MOSI*      | Bi-<br>directional | The signal is an output if the SPI core is in Master mode (SISPI). The signal is an input if the SPI core is in Slave mode (SI). This signal could use dedicated I/O pin.                                                                                            |

| SPx_MISO*      | Bi-<br>directional | The signal is an input if the SPI core is in Master mode (SPISO). The signal is an output if the SPI core is in Slave mode (SO). This signal could use dedicated I/O pin.                                                                                            |

| SPx_SCSN*      | I                  | User Slave Chip Select (Active Low). An external SPI Master controller asserts this signal to transfer data to/from the SPI Controllers Transmit Data/Receive Data registers. This signal could use dedicated I/O pin. The dedicated pin is shared with SPI_MCSN[0]. |

| SPx_MCSN[3:0]* | 0                  | Master Chip Select (Active Low). Up to 4 independent slave SPI devices can be accessed using the SPI Controller when it is in Master SPI mode. Only SPI_MCSN[0] could use dedicated I/O pin.                                                                         |

#### Table 8.1. Pins for the Hard SPI IP

**\*Note:** x indicates the SPI: x=1 for the left SPI; x=2 for the right SPI.

## 9. iCE40LM, iCE40 Ultra, and iCE40 UltraPlus SPI Usage Cases

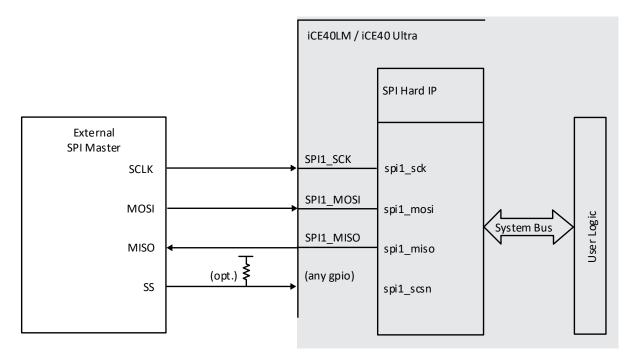

The SPI usage cases described below refer to Figure 9.1 and Figure 9.2.

- 1. External Master SPI Device Accessing the Slave iCE40LM, iCE40 Ultra and iCE40 UltraPlus User SPI

- a. The External Master SPI is connected to the iCE40LM, iCE40 Ultra and iCE40 UltraPlus using the dedicated SI, SO, CCLK pins. The spi\_scsn is placed on any Generic I/O. The SPI Mode is set to Slave only.

- b. A Master controller is implemented in the general purpose logic array. The master controller monitors the availability to transmit or receive data by polling the SPI status registers, or by responding to interrupts generated by the SPI Controller.

#### Figure 9.1. External Master SPI Device Accessing the Slave User SPI

- 2. iCE40LM, iCE40 Ultra and iCE40 UltraPlus user SPI Master accessing one or multiple External Slave SPI devices

- a. The iCE40LM, iCE40 Ultra and iCE40 UltraPlus Master is connected to External SPI Slave devices. The Chip Selects are configured as follows:

- i. The iCE40LM, iCE40 Ultra and iCE40 UltraPlus SPI Master Chip Select spi\_mcsn[0] is placed on the dedicated CSSPIN and connected to the External Slave Chip Select.

- ii. The iCE40LM, iCE40 Ultra and iCE40 UltraPlus SPI Master Chip Select spi\_mcsn[1] is placed on any I/O and connected to another External Slave Chip Select.

- iii. Up to 4 External Slave SPIs can be connected using spi\_mcsn[3:0].

- b. A Master controller is implemented in the iCE40LM, iCE40 Ultra and iCE40 UltraPlus general logic. It controls transfers to the slave SPI devices. It can use a polling method, or it can use SPI Controller interrupts to manage transfer and reception of data.

Figure 9.2. iCE40LM, iCE40 Ultra and iCE40 UltraPlus User SPI Master Accessing One or Multiple External Slave SPI Devices

## **10. Module Generator**

The iCE40LM, iCE40 Ultra and iCE40 UltraPlus use a System Bus to connect its Hard IP to the fabric. The System bus is connected to two SPI and two I<sup>2</sup>C Hard IPs. The iCE40LM, iCE40 Ultra and iCE40 UltraPlus devices do not preload the Hard IP registers during configuration, so a soft IP will be required.

### **10.1. Key Features**

- Module Generator will generate the Soft IP which is a wrapper around the Hard IP.

- Soft IP will release the System Bus after the Hard IPs have been configured.

- The Soft IP by default will use the HSSG for iCE40LM and use SB\_HFOSC for iCE40 Ultra and iCE40 UltraPlus. For details on HSSG, refer to iCE40LM On-Chip Strobe Generator Usage Guide (FPGA-TN-02212). For details on SB\_HFOSC, refer to iCE40 Oscillator Usage Guide (FPGA-TN-02008).

- The Register file will be [9:256].

- The address size is 256 bits which encompasses all address of the Hard IPs.

- The data size is 9 bits with the format [W, Register Data]. When W=1 the state machine will write the corresponding Hard IP address with data.

See Advanced iCE40 I<sup>2</sup>C and SPI Hardened IP Usage Guide (FPGA-TN-02011) for more information.

Notes: Only SPI\*\_MSCN[1:0] have dedicated pins

IPDONE = 1 when Hard IP Configuration is complete, IPDONE = 0 during configuration IPLOAD is an in put signal which is used to begin configuration on a positive edge

Figure 10.1. Soft IP Block Diagram

| I2C/SPI Module | Generator  Generate Log  Hard IP Enables I2C SPI  Enable Hard User IPS  Enable hard user I2C left  Enable hard user SPI left  Enable hard user SPI left  System Clock System bus clock frequency MHz  Configuration Clock Source  High speed Strobe Generator (HSSG)  User clock |       |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|                | Generate                                                                                                                                                                                                                                                                         | Close |

Figure 10.2. Module Generator

### 10.1.1. Enable Left I<sup>2</sup>C

This option allows the user to enable left I<sup>2</sup>C on the I<sup>2</sup>C Tab

### 10.1.2. Enable Right I<sup>2</sup>C

This option allows the user to enable right I<sup>2</sup>C on the I<sup>2</sup>C Tab

### 10.1.3. Enable Left SPI

This option allows the user to enable left SPI on the SPI Tab

### 10.1.4. Enable Right SPI

This option allows the user to enable right SPI on the SPI Tab

### 10.1.5. System Clock

User setting which is used to set the divider settings of the I<sup>2</sup>C and SPI

### 10.1.6. Configuration Clock Source

User will select to use the HSSG/SB\_HFOSC or the CLKCONF (User provided clock). For details, refer to iCE40LM On-Chip Strobe Generator Usage Guide (FPGA-TN-02212) for HSSG and iCE40 Oscillator Usage Guide (FPGA-TN-02088) for SB\_HFOSC.

## **Technical Support Assistance**

Submit a technical support case through www.latticesemi.com/techsupport.

## **Revision History**

#### Revision 1.7, August 2020

| Section                        | Change Summary                                                                       |

|--------------------------------|--------------------------------------------------------------------------------------|

| SB_I2C Hard IP Macro Ports and | Changed pin direction of SBWRi and SBSTBi in Table 4.1. Pins for the Hard I2C IP for |

| Wrapper Connections            | iCE40LM, iCE40 Ultra, and iCE40 UltraPlus.                                           |

#### Revision 1.6, May 2020.

| Section                                               | Change Summary                                                                                                                                                              |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Disclaimers                                           | Added this section.                                                                                                                                                         |

| SB_I2C Hard IP Macro Ports and<br>Wrapper Connections | Changed SBWRi and SBSTBi pin direction to Input in Table 4.2. Pins for the Hard I2C IP for iCE40 UltraLite.                                                                 |

| All                                                   | <ul> <li>Updated document number of referenced technical note.</li> <li>Updated format of revision history and back cover.</li> <li>Minor adjustments in styles.</li> </ul> |

#### Revision 1.5, August 2017

| Section                    | Change Summary                                                              |

|----------------------------|-----------------------------------------------------------------------------|

| All                        | Changed document number from TN1274 to FPGA-TN-02010.                       |

|                            | Updated document template.                                                  |

|                            | <ul> <li>Updated document numbers of referenced technical notes.</li> </ul> |

| Acronyms in This Documents | Added this section.                                                         |

#### Revision 1.4, June 2016

| Section                                               | Change Summary                                                                                                                                     |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| All                                                   | Added support for iCE40 UltraPlus.                                                                                                                 |

| Disclaimers                                           | Updated Introduction section.                                                                                                                      |

|                                                       | Revised introductory paragraph and description of key components.                                                                                  |

|                                                       | • Revised figure caption to Figure 1.1. IP Block Diagram for iCE40LM, iCE40 Ultra, and ICE40 UltraPlus.                                            |

| I <sup>2</sup> C IP Core Overview                     | Updated I <sup>2</sup> C IP Core Overview section. Revised heading to Key Features for iCE40LM, iCE40 Ultra, and iCE40 UltraPlus.                  |

| I <sup>2</sup> C Usage with Module                    | Updated I <sup>2</sup> C Usage with Module Generation section.                                                                                     |

| Generation                                            | • Revised figure caption to Figure 3.1. I <sup>2</sup> C Module GUI for iCE40LM, iCE40 Ultra, and iCE40 UltraPlus.                                 |

|                                                       | • Revised figure caption to Figure 3.2. I <sup>2</sup> C Module GUI for iCE40 UltraLite.                                                           |

| SB_I2C Hard IP Macro Ports and<br>Wrapper Connections | Updated SB_I2C Hard IP Macro Ports and Wrapper Connections section.                                                                                |

|                                                       | • Revised table caption to Table 4.1. Pins for the Hard I <sup>2</sup> C IP for iCE40LM, iCE40 Ultra, and iCE40 UltraPlus.                         |

|                                                       | • Revised table caption to Table 4.2. Pins for the Hard I <sup>2</sup> C IP for iCE40UltraLite                                                     |

| SPI Usage with Module                                 | Updated SPI Usage with Module Generation section.                                                                                                  |

| Generation                                            | • Revised figure caption to Figure 7.1. SPI Module GUI for iCE40LM, iCE40 Ultra, and iCE40 UltraPlus.                                              |

| iCE40LM, iCE40 Ultra, and iCE40                       | Updated iCE40LM, iCE40 Ultra, and iCE40 UltraPlus SPI Usage Cases section.                                                                         |

| UltraPlus SPI Usage Cases                             | Revised section heading to include iCE40 UltraPlus.                                                                                                |

|                                                       | Revised use cases to include iCE40 UltraPlus.                                                                                                      |

|                                                       | Added iCE40 UltraPlus to Figure 9.1. External Master SPI Device Accessing the Slave User SPI.                                                      |

|                                                       | Added iCE40 UltraPlus to Figure 9.2. iCE40LM, iCE40 Ultra and iCE40 UltraPlus User SPI Master Accessing One or Multiple External Slave SPI Devices |

| Module Generator                                      | Updated Module Generator section. Added iCE40 UltraPlus to introductory paragraph and Key Features.                                                |

| Section                      | Change Summary                                |

|------------------------------|-----------------------------------------------|

| Technical Support Assistance | Updated Technical Support Assistance section. |

#### Revision 1.3, January 2015

| Section | Change Summary                     |

|---------|------------------------------------|

| All     | Added support for iCE40 UltraLite. |

#### Revision 1.2, June 2014

| Section | Change Summary                                                                      |

|---------|-------------------------------------------------------------------------------------|

| All     | • Changed document title to iCE40 I <sup>2</sup> C and SPI Hardened IP Usage Guide. |

|         | Added support for iCE40 Ultra.                                                      |

#### Revision 1.1, November 2013

| Section          | Change Summary                                              |

|------------------|-------------------------------------------------------------|

| All              | Changed hard IP pin names.                                  |

| Module Generator | Updated screen captures of Module Generator user interface. |

#### Revision 1.0, October 2013

| Section | Change Summary   |

|---------|------------------|

| All     | Initial release. |

www.latticesemi.com