feat(SinaraCore): Adds origin image to display when click

This commit is contained in:

parent

ecc932a8dd

commit

1cf850e562

content/experiment-control

static/images/origin

@ -8,7 +8,7 @@ title = "Sinara hardware"

|

||||

+++

|

||||

|

||||

|

||||

{% layout_text_img(src="images/sinara-hardware@2x.png", alt="", textleft=true, shadow=false) %}

|

||||

{% layout_text_img(src="images/sinara-hardware@2x.png", popup="images/origin/sinara_hardware.jpg", alt="", textleft=true, shadow=false) %}

|

||||

|

||||

The first ARTIQ core devices used hardware built in-house by physicists (based on a Xilinx KC705 development board with custom FMC cards). To improve the quality, features and scalability of ARTIQ systems, we have been developing the Sinara device family. It aims at providing turnkey control hardware that is reproducible, open, flexible, modular, well-tested, and well-supported by the ARTIQ control software.

|

||||

|

||||

@ -20,7 +20,7 @@ Kasli and EEMs can be ordered now. We can deliver a rack-mountable crate that co

|

||||

|

||||

|

||||

|

||||

{% layout_text_img(src="images/kasli@2x.png", alt="", shadow=false) %}

|

||||

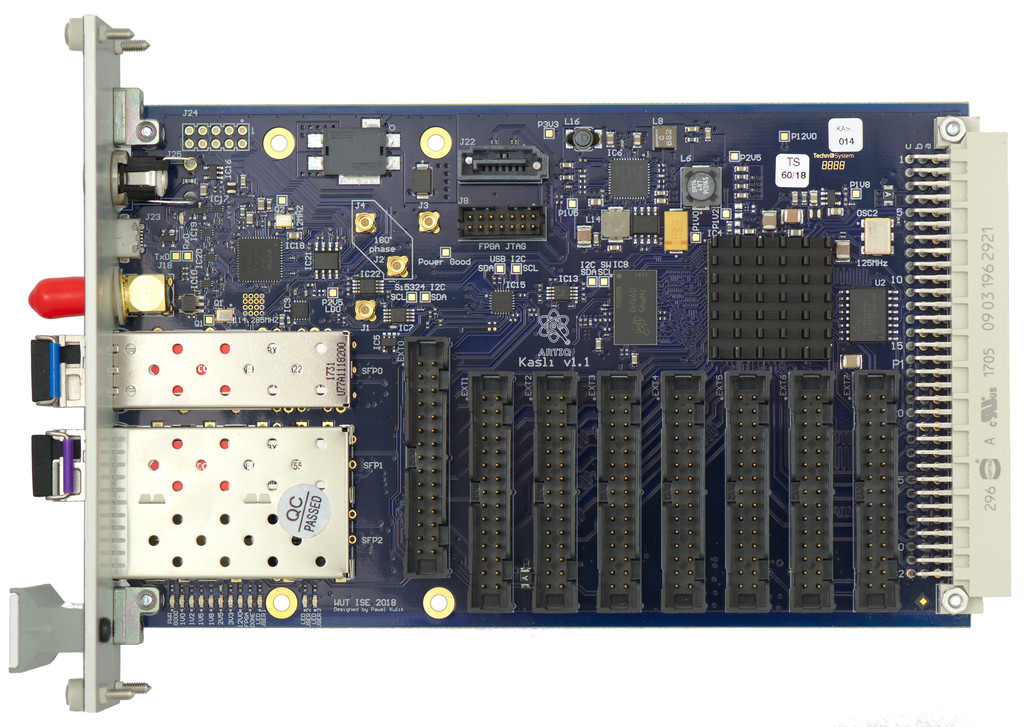

{% layout_text_img(src="images/kasli@2x.png", popup="images/origin/kasli.jpg", alt="", shadow=false) %}

|

||||

|

||||

##### Kasli

|

||||

|

||||

@ -32,7 +32,7 @@ One of the main devices in the Sinara family is the Kasli core device. It contai

|

||||

|

||||

|

||||

|

||||

{% layout_text_img(src="images/isolated-ttl@2x.png", alt="", textleft=true, shadow=false) %}

|

||||

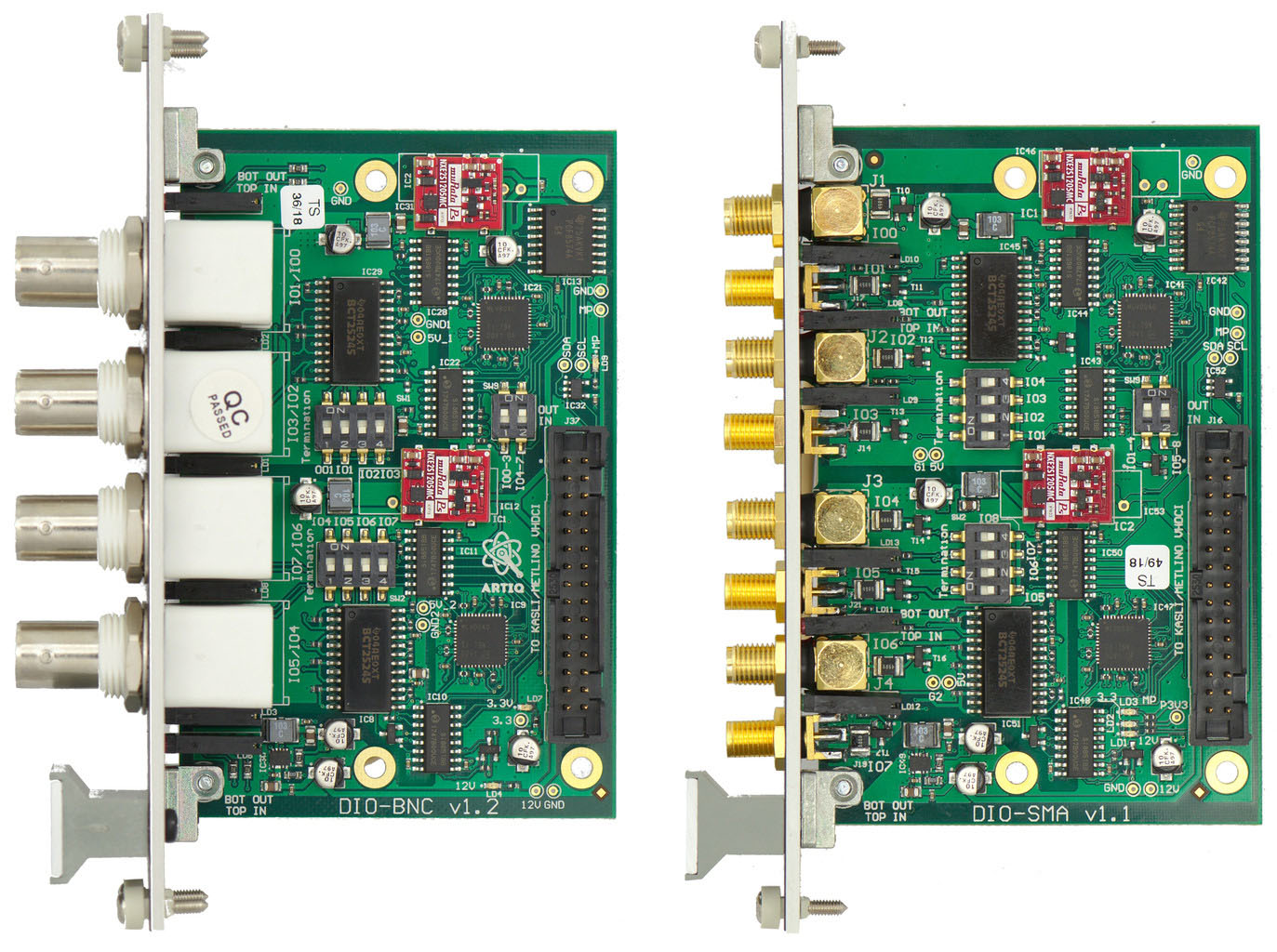

{% layout_text_img(src="images/isolated-ttl@2x.png", popup="images/origin/dio.jpg", alt="", textleft=true, shadow=false) %}

|

||||

|

||||

##### Isolated TTL I/O EEMs

|

||||

|

||||

@ -44,7 +44,7 @@ More information: <a href="https://github.com/sinara-hw/DIO_BNC/wiki" target="_b

|

||||

|

||||

|

||||

|

||||

{% layout_text_img(src="images/LVDS@2x.png", alt="", shadow=false) %}

|

||||

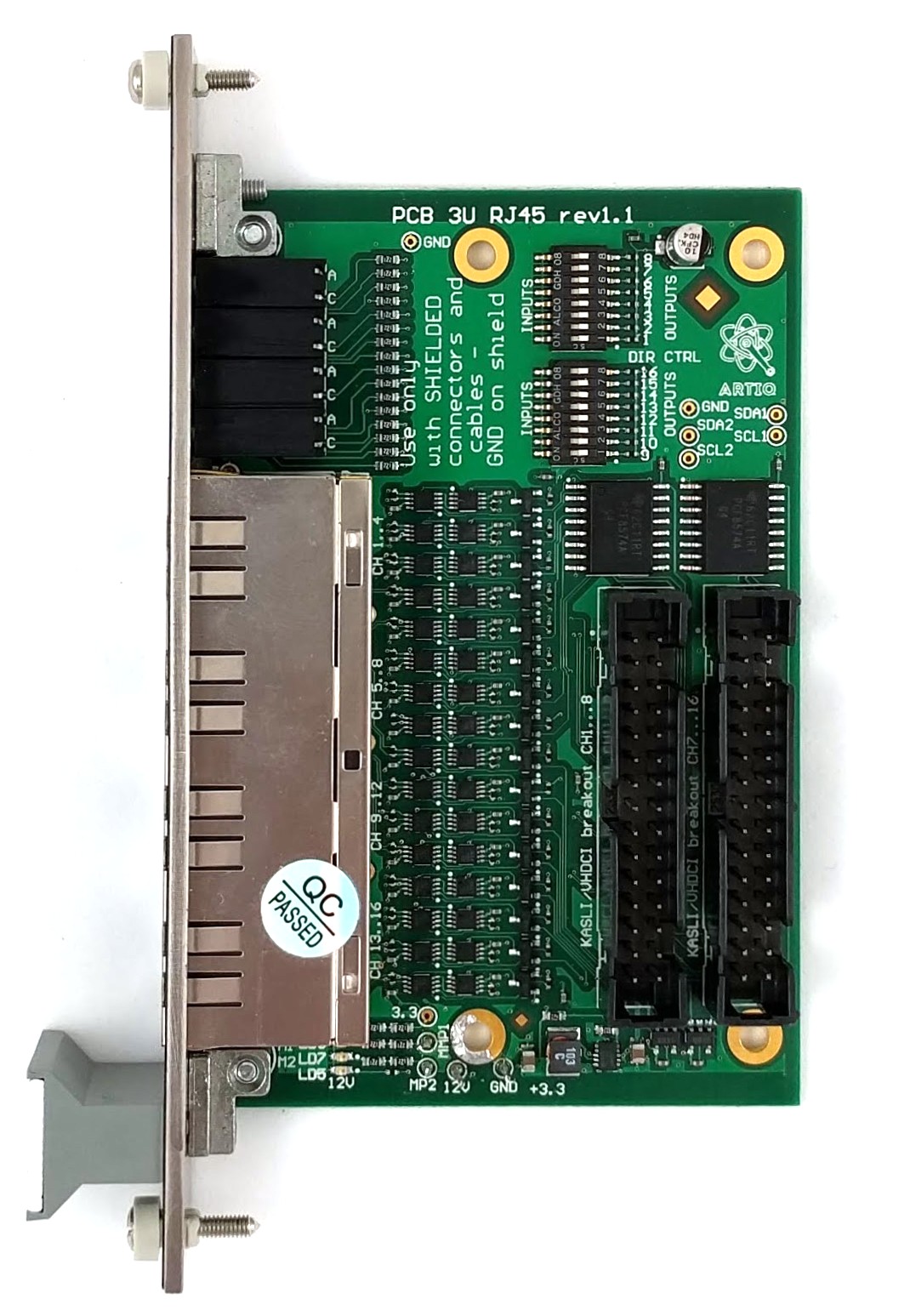

{% layout_text_img(src="images/LVDS@2x.png", popup="images/origin/dio_rj45.jpg", alt="", shadow=false) %}

|

||||

|

||||

##### LVDS I/O EEM

|

||||

|

||||

@ -57,7 +57,7 @@ Each RJ45 supplies 4 LVDS DIOs. The direction (input/output) is individually sel

|

||||

|

||||

|

||||

|

||||

{% layout_text_img(src="images/Banker-TTL-1@2x.png", alt="", textleft=true, shadow=false) %}

|

||||

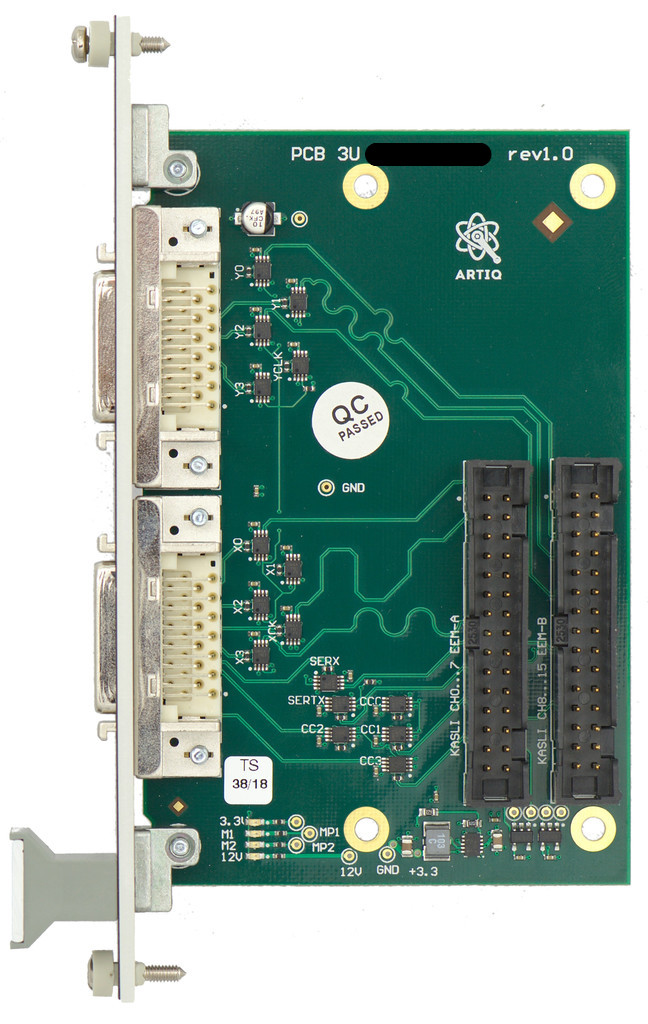

{% layout_text_img(src="images/Banker-TTL-1@2x.png", popup="images/origin/banker1.jpg", alt="", textleft=true, shadow=false) %}

|

||||

|

||||

##### Banker 128-channel TTL I/O expander

|

||||

|

||||

@ -73,7 +73,7 @@ Interfaces include:

|

||||

|

||||

|

||||

|

||||

{% layout_text_img(src="images/Banker-TTL-2@2x.png", alt="", textleft=true, shadow=false) %}

|

||||

{% layout_text_img(src="images/Banker-TTL-2@2x.png", popup="images/origin/banker2.jpg", alt="", textleft=true, shadow=false) %}

|

||||

|

||||

All outputs can be configured either as 3.3 or 5V. They can drive 50R load when set to 5V. FPGA can is configured from on-board FLASH. FLASH can be updated over I2C or with the on-board SPI connector.

|

||||

|

||||

@ -92,7 +92,7 @@ There are several DIN-rail compatible modules for use with Banker. They are inte

|

||||

|

||||

|

||||

|

||||

{% layout_text_img(src="images/Urukul-DDS@2x.png", alt="", shadow=false) %}

|

||||

{% layout_text_img(src="images/Urukul-DDS@2x.png", popup="images/origin/urukul.jpg", alt="", shadow=false) %}

|

||||

|

||||

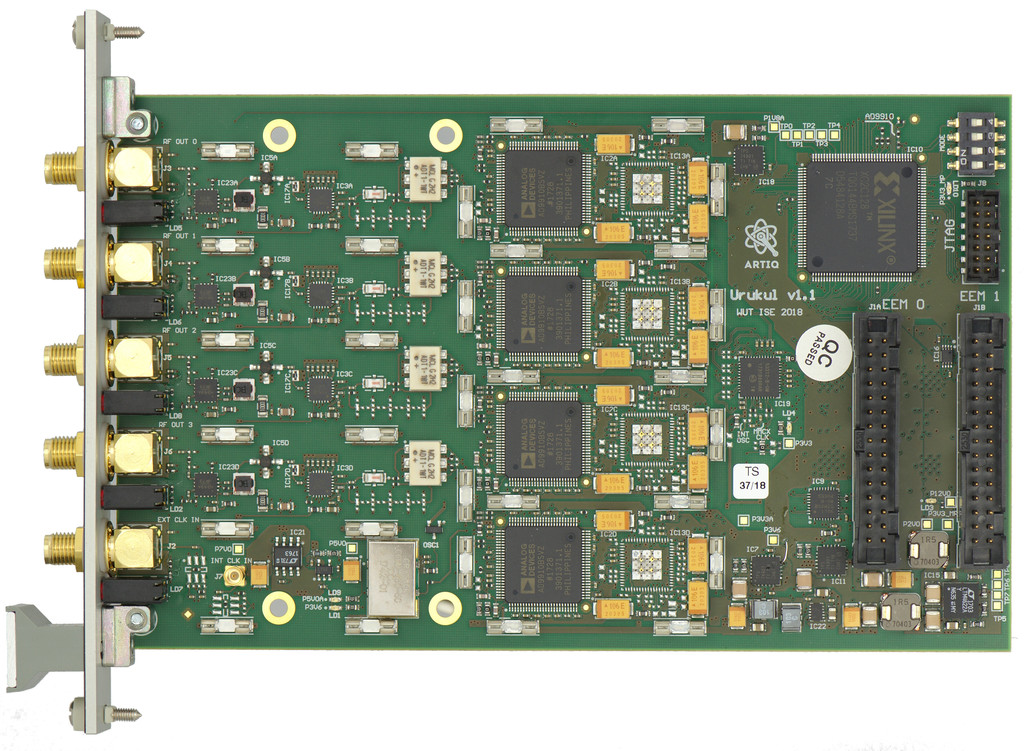

##### Urukul DDS card

|

||||

|

||||

@ -108,7 +108,7 @@ In regular mode, various DDS features are supported, including frequency, phase

|

||||

|

||||

|

||||

|

||||

{% layout_text_img(src="images/Zotino-DAC@2x.png", alt="", textleft=true, shadow=false) %}

|

||||

{% layout_text_img(src="images/Zotino-DAC@2x.png", popup="images/origin/zotino.jpg", alt="", textleft=true, shadow=false) %}

|

||||

|

||||

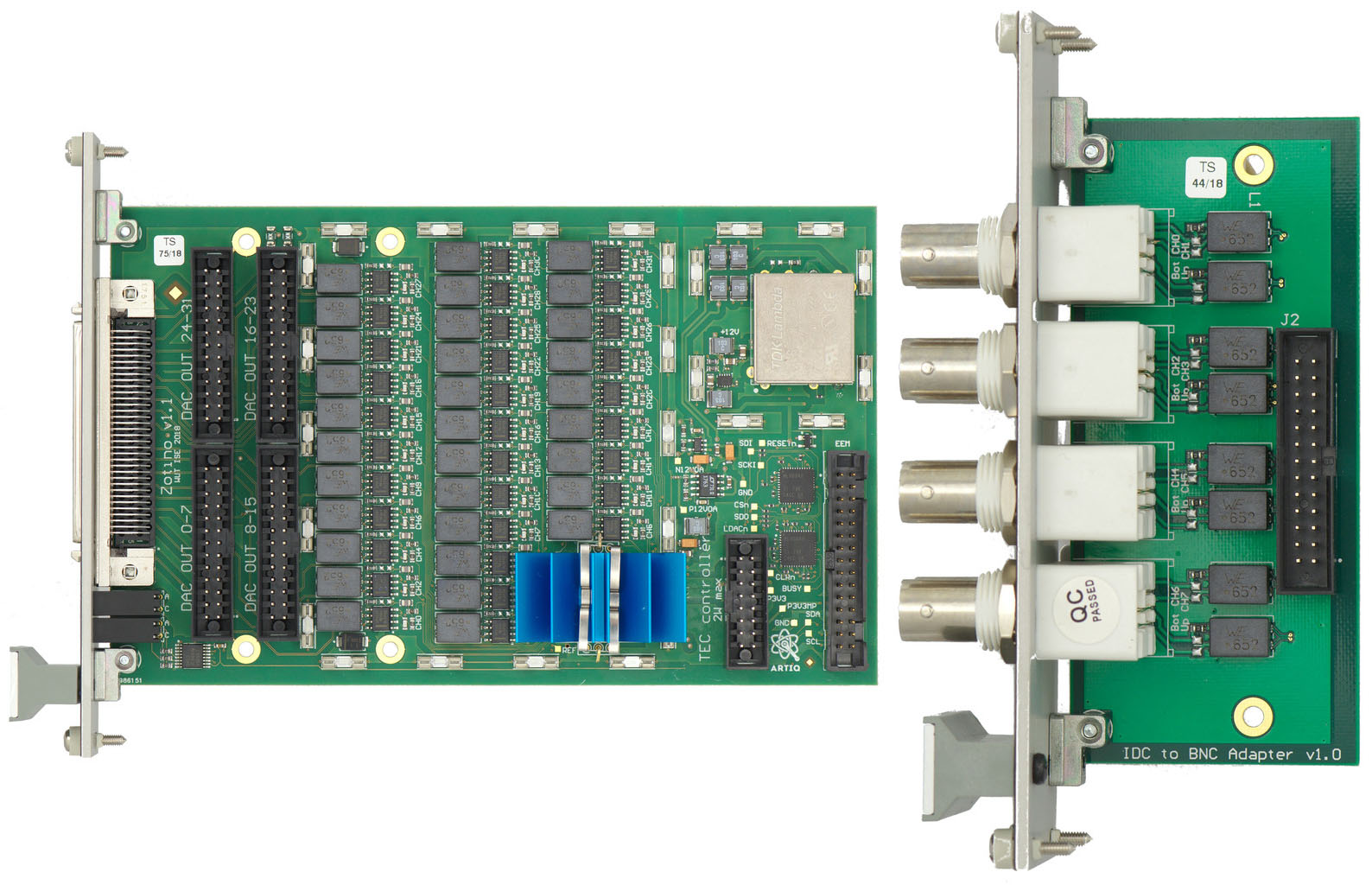

##### Zotino DAC card

|

||||

|

||||

@ -124,7 +124,7 @@ It is also possible to connect the Zotino using a HD68 cable to an external crat

|

||||

|

||||

|

||||

|

||||

{% layout_text_img(src="images/Sampler-ADC@2x.png", alt="", shadow=false) %}

|

||||

{% layout_text_img(src="images/Sampler-ADC@2x.png", popup="images/origin/sampler.jpg", alt="", shadow=false) %}

|

||||

|

||||

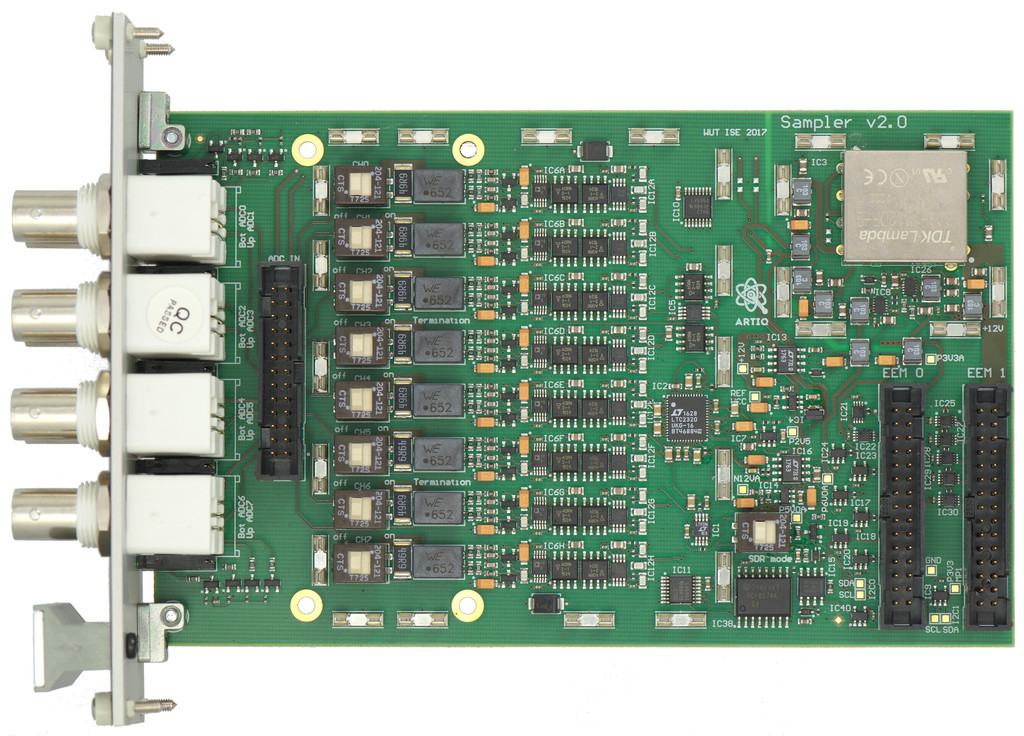

##### Sampler ADC card

|

||||

|

||||

@ -140,7 +140,7 @@ Note that update rate specification on this page is for the hardware only; ARTIQ

|

||||

|

||||

|

||||

|

||||

{% layout_text_img(src="images/Grabber-camera-interface@2x.png", alt="", textleft=true, shadow=false) %}

|

||||

{% layout_text_img(src="images/Grabber-camera-interface@2x.png", popup="images/origin/grabber.jpg", alt="", textleft=true, shadow=false) %}

|

||||

|

||||

##### Grabber camera interface

|

||||

|

||||

@ -154,7 +154,7 @@ In the FPGA, frame data streamed through "ROI engines". Each ROI engine gates on

|

||||

|

||||

|

||||

|

||||

{% layout_text_img(src="images/clocker@2x.png", alt="", shadow=false) %}

|

||||

{% layout_text_img(src="images/clocker@2x.png", popup="images/origin/clocker.jpg", alt="", shadow=false) %}

|

||||

|

||||

##### Clocker

|

||||

|

||||

|

||||

BIN

static/images/origin/banker1.jpg

Normal file

BIN

static/images/origin/banker1.jpg

Normal file

Binary file not shown.

|

After

(image error) Size: 292 KiB |

BIN

static/images/origin/banker2.jpg

Normal file

BIN

static/images/origin/banker2.jpg

Normal file

Binary file not shown.

|

After

(image error) Size: 234 KiB |

BIN

static/images/origin/clocker.jpg

Normal file

BIN

static/images/origin/clocker.jpg

Normal file

Binary file not shown.

|

After

(image error) Size: 257 KiB |

BIN

static/images/origin/dio.jpg

Normal file

BIN

static/images/origin/dio.jpg

Normal file

Binary file not shown.

|

After

(image error) Size: 360 KiB |

BIN

static/images/origin/dio_rj45.jpg

Normal file

BIN

static/images/origin/dio_rj45.jpg

Normal file

Binary file not shown.

|

After

(image error) Size: 300 KiB |

BIN

static/images/origin/grabber.jpg

Normal file

BIN

static/images/origin/grabber.jpg

Normal file

Binary file not shown.

|

After

(image error) Size: 228 KiB |

BIN

static/images/origin/kasli.jpg

Normal file

BIN

static/images/origin/kasli.jpg

Normal file

Binary file not shown.

|

After

(image error) Size: 266 KiB |

BIN

static/images/origin/sampler.jpg

Normal file

BIN

static/images/origin/sampler.jpg

Normal file

Binary file not shown.

|

After

(image error) Size: 303 KiB |

BIN

static/images/origin/sinara_hardware.jpg

Normal file

BIN

static/images/origin/sinara_hardware.jpg

Normal file

Binary file not shown.

|

After

(image error) Size: 937 KiB |

BIN

static/images/origin/urukul.jpg

Normal file

BIN

static/images/origin/urukul.jpg

Normal file

Binary file not shown.

|

After

(image error) Size: 319 KiB |

BIN

static/images/origin/zotino.jpg

Normal file

BIN

static/images/origin/zotino.jpg

Normal file

Binary file not shown.

|

After

(image error) Size: 289 KiB |

Loading…

Reference in New Issue

Block a user