# Migen manual

Release X

Sebastien Bourdeauducq

August 12, 2012

# CONTENTS

| 1 | <b>Intro</b> 1.1 1.2 1.3 | Background                                | 1<br>1<br>2<br>2 |  |  |  |  |  |  |  |

|---|--------------------------|-------------------------------------------|------------------|--|--|--|--|--|--|--|

| 2 | The 1                    | FHDL layer                                | 3                |  |  |  |  |  |  |  |

|   | 2.1                      | Expressions                               | 3                |  |  |  |  |  |  |  |

|   |                          | 2.1.1 Bit vector (BV)                     | 3                |  |  |  |  |  |  |  |

|   |                          |                                           | 3                |  |  |  |  |  |  |  |

|   |                          |                                           | 4                |  |  |  |  |  |  |  |

|   |                          | 2.1.4 Operators                           | 4                |  |  |  |  |  |  |  |

|   |                          |                                           | 4                |  |  |  |  |  |  |  |

|   |                          |                                           | 5                |  |  |  |  |  |  |  |

|   |                          | 1                                         | 5                |  |  |  |  |  |  |  |

|   | 2.2                      |                                           | 5                |  |  |  |  |  |  |  |

|   |                          |                                           | 5                |  |  |  |  |  |  |  |

|   |                          |                                           | 5                |  |  |  |  |  |  |  |

|   |                          |                                           | 6                |  |  |  |  |  |  |  |

|   | 0.0                      |                                           | 6                |  |  |  |  |  |  |  |

|   | 2.3                      | 1                                         | 6                |  |  |  |  |  |  |  |

|   |                          |                                           | 6<br>7           |  |  |  |  |  |  |  |

|   | 2.4                      |                                           | 7<br>8           |  |  |  |  |  |  |  |

|   | 2.4                      |                                           | 8<br>8           |  |  |  |  |  |  |  |

|   | 2.5                      | Conversion for synthesis                  | ð                |  |  |  |  |  |  |  |

| 3 | Bus s                    | support                                   | 9                |  |  |  |  |  |  |  |

|   | 3.1                      | Configuration and Status Registers        | 9                |  |  |  |  |  |  |  |

|   |                          | 3.1.1 CSR-2 bus                           | 9                |  |  |  |  |  |  |  |

|   |                          | 3.1.2 Generating register banks           | 0                |  |  |  |  |  |  |  |

|   |                          | 3.1.3 Generating interrupt controllers    | 0                |  |  |  |  |  |  |  |

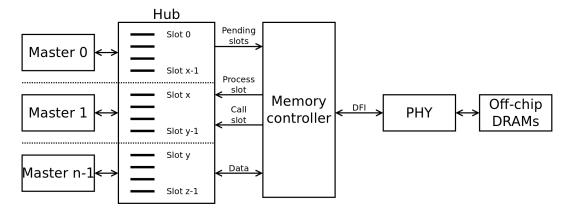

|   | 3.2                      | Advanced System Memory Infrastructure     |                  |  |  |  |  |  |  |  |

|   |                          | 3.2.1 Rationale                           |                  |  |  |  |  |  |  |  |

|   |                          | 3.2.2 Topology                            |                  |  |  |  |  |  |  |  |

|   |                          | 3.2.3 Signals                             |                  |  |  |  |  |  |  |  |

|   |                          | 3.2.4 SDRAM burst length and clock ratios |                  |  |  |  |  |  |  |  |

|   |                          | 3.2.5 Using ASMI with Migen               | 3                |  |  |  |  |  |  |  |

| 4 | Dataflow 15              |                                           |                  |  |  |  |  |  |  |  |

| - | 4.1                      | Actors                                    |                  |  |  |  |  |  |  |  |

|   |                          |                                           |                  |  |  |  |  |  |  |  |

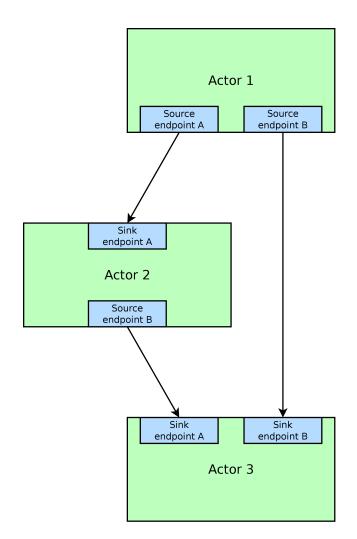

|   |                                                                                           | 4.1.1 Actors and endpoints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                 |

|---|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                           | 4.1.2 Busy signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                                                           | 4.1.3 Common scheduling models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                                                           | Combinatorial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                                                           | N-sequential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | N-pipelined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 4.2                                                                                       | The Migen actor library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | 4.2.1 Plumbing actors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | Combinator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | Splitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | 4.2.2 Structuring actors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | Cast                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | Pack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | 4.2.3 Simulation actors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | 4.2.4 Arithmetic and logic actors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | 4.2.5 Bus actors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | Wishbone reader                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | Wishbone writer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                                                           | ASMI reader                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                                                           | ASMI writer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                                                           | 4.2.6 Miscellaneous actors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                                                           | Integer sequence generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 4.3                                                                                       | Actor networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                                                           | 4.3.1 Graph definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | 4.3.2 Abstract and physical networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                                                           | 1 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                           | 4.3.3 Elaboration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 4.4                                                                                       | 4.3.3       Elaboration         4.3.4       Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | · · · 22<br>· · · 23                                                                                                                                                                                                                                                                                                                                                                               |

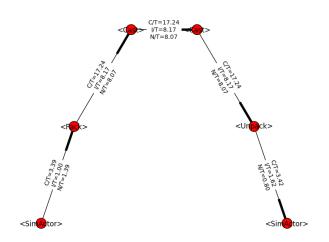

|   | 4.4<br>4.5                                                                                | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | · · · 22<br>· · · 23<br>· · · 23                                                                                                                                                                                                                                                                                                                                                                   |

|   | 4.4<br>4.5                                                                                | 4.3.3       Elaboration         4.3.4       Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | · · · 22<br>· · · 23<br>· · · 23                                                                                                                                                                                                                                                                                                                                                                   |

| 5 | 4.5                                                                                       | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools          High-level actor description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | · · · 22<br>· · · 23<br>· · · 23                                                                                                                                                                                                                                                                                                                                                                   |

| 5 | 4.5                                                                                       | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools          High-level actor description          ulating a Migen design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22<br>23<br>23<br>23<br><b>25</b>                                                                                                                                                                                                                                                                                                                                                                  |

| 5 | 4.5<br>Simu<br>5.1                                                                        | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools          High-level actor description          ulating a Migen design       Installing the VPI module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22<br>23<br>23<br>23<br>23<br>25<br>25                                                                                                                                                                                                                                                                                                                                                             |

| 5 | 4.5<br>Simu                                                                               | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools          High-level actor description          ulating a Migen design         Installing the VPI module         The generic simulator object                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22<br>23<br>23<br>23<br>23<br>25<br>25<br>25                                                                                                                                                                                                                                                                                                                                                       |

| 5 | 4.5<br>Simu<br>5.1                                                                        | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools          High-level actor description          ulating a Migen design         Installing the VPI module         The generic simulator object         5.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22<br>23<br>23<br>23<br>23<br>25<br>25<br>25<br>25                                                                                                                                                                                                                                                                                                                                                 |

| 5 | 4.5<br>Simu<br>5.1                                                                        | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools          High-level actor description          ulating a Migen design          Installing the VPI module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22          23          23          23          23          25          25          25          25          25          25          25          25          25          26                                                                                                                                                                                                                         |

| 5 | 4.5<br>Simu<br>5.1                                                                        | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools          High-level actor description          ulating a Migen design          Installing the VPI module          5.2.1       Creating a simulator object         5.2.2       Running the simulation         5.2.3       Reading and writing signals                                                                                                                                                                                                                                                                                                                                                                                                                   | 22          23          23          23          23          25          25          25          25          25          25          25                                                                                                                                                                                                                                                             |

| 5 | 4.5<br>Simu<br>5.1                                                                        | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22<br>23<br>23<br>23<br>25<br>25<br>25<br>26<br>26<br>26<br>26                                                                                                                                                                                                                                                                                                                                     |

| 5 | 4.5<br>Simu<br>5.1<br>5.2                                                                 | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22          23          23          23          23          23          25          25          25          25          25          25          26          26          26          26          26                                                                                                                                                                                                 |

| 5 | 4.5<br>Simu<br>5.1                                                                        | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools          High-level actor description          ulating a Migen design          Installing the VPI module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22          23          23          23          23          23          25          25          25          25          25          26          26          26          26          26          26          26          26          27                                                                                                                                                             |

| 5 | 4.5<br>Simu<br>5.1<br>5.2                                                                 | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22          23          23          23          23          23          23          23          25          25          25          26          26          26          26          26          26          26          27          27                                                                                                                                                             |

| 5 | <ul><li>4.5</li><li>Simu</li><li>5.1</li><li>5.2</li><li>5.3</li></ul>                    | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools          High-level actor description          ulating a Migen design          Installing the VPI module          The generic simulator object          5.2.1       Creating a simulator object         5.2.2       Running the simulation         5.2.3       Reading and writing signals         5.2.4       Reading and writing memories         5.2.5       Initializing signals and memories         5.2.1       Reading and writing memories         5.2.3       Reading and writing memories         5.2.4       Reading and memories         5.2.5       Initializing signals and memories         5.3.1       Role         5.3.2       Icarus Verilog support | 22          23          23          23          23          23          25          25          25          25          25          26          26          26          26          26          26          26          26          27          27          27          27                                                                                                                         |

| 5 | 4.5<br>Simu<br>5.1<br>5.2                                                                 | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22          23          23          23          23          23          25          25          25          26          26          26          26          26          26          26          26          26          27          27          27                                                                                                                                                 |

| 5 | <ul><li>4.5</li><li>Simu</li><li>5.1</li><li>5.2</li><li>5.3</li></ul>                    | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22          23          23          23          23          23          23          23          23          25          25          25          26          26          26          26          26          26          27          27          27          27          27          27          27          27          27                                                                         |

| 5 | <ul><li>4.5</li><li>Simu</li><li>5.1</li><li>5.2</li><li>5.3</li></ul>                    | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22          23          23          23          23          23          23          23          23          25          25          25          26          26          26          26          26          26          27          27          27          27          27          27          27          27          27          27          27          27                                     |

| 5 | <ul> <li>4.5</li> <li>Simu</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul> | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22          23          23          23          23          23          23          23          23          23          23          25          25          25          25          25          25          25          25          25          25          26          26          27          27          27          27          27          27          27          27          27          28 |

| 5 | <ul><li>4.5</li><li>Simu</li><li>5.1</li><li>5.2</li><li>5.3</li></ul>                    | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22          23          23          23          23          23          23          23          23          25          25          25          26          26          26          26          26          27          27          27          27          27          27          27          27          27          27          28          28                                                 |

| 5 | <ul> <li>4.5</li> <li>Simu</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul> | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22          23          23          23          23          23          23          23          23          25          25          25          26          26          26          26          26          26          27          27          27          27          27          27          27          27          27                                                                         |

| 5 | <ul> <li>4.5</li> <li>Simu</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul> | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22          23          23          23          23          23          23          23          23          25          25          25          26          26          26          26          26          26          26          27          27          27          27          27          27          27          27                                                                         |

| 5 | <ul> <li>4.5</li> <li>Simu</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul> | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22          23          23          23          23          23          23          23          23          25          25          25          26          26          26          26          26          26          26          26          27          27          27          27          27          28          28          28                                                             |

| 5 | <ul> <li>4.5</li> <li>Simu</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul> | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22          23          23          23          23          23          23          23          23          25          25          25          26          26          26          26          26          26          27          27          27          27          27          27          27          28          28          28                                                             |

| 5 | <ul> <li>4.5</li> <li>Simu</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul> | 4.3.3       Elaboration         4.3.4       Implementation         Performance tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22          23          23          23          23          23          23          23          23          25          25          25          25          25          25          25          26          26          26          26          27          27          27          27          27          27          28          28          28          28          30          30          32 |

| · · | 0000 | studies |                        |

|-----|------|---------|------------------------|

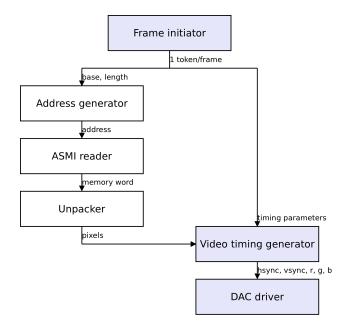

|     | 6.1  | A VGA   | framebuffer core       |

|     |      | 6.1.1   | Purpose                |

|     |      | 6.1.2   | Architecture           |

|     |      | 6.1.3   | Frame initiator        |

|     |      | 6.1.4   | Pixel fetcher          |

|     |      | 6.1.5   | Video timing generator |

|     |      | 6.1.6   | DAC driver             |

## Bibliography

37

# INTRODUCTION

Migen is a Python-based tool that aims at automating further the VLSI design process.

Migen makes it possible to apply modern software concepts such as object-oriented programming and metaprogramming to design hardware. This results in more elegant and easily maintained designs and reduces the incidence of human errors.

# 1.1 Background

Even though the Milkymist system-on-chip [mm] is technically successful, it suffers from several limitations stemming from its implementation in manually written Verilog HDL:

- 1. The "event-driven" paradigm of today's dominant hardware descriptions languages (Verilog and VHDL, collectively referred to as "V\*HDL" in the rest of this document) is often too general. Today's FPGA architectures are optimized for the implementation of fully synchronous circuits. This means that the bulk of the code for an efficient FPGA design falls into three categories:

- (a) Combinatorial statements

- (b) Synchronous statements

- (c) Initialization of registers at reset

V\*HDL do not follow this organization. This means that a lot of repetitive manual coding is needed, which brings sources of human errors, petty issues, and confusion for beginners:

- (a) wire vs. reg in Verilog

- (b) forgetting to initialize a register at reset

- (c) deciding whether a combinatorial statement must go into a process/always block or not

- (d) simulation mismatches with combinatorial processes/always blocks

- (e) and more...

A little-known fact about FPGAs is that many of them have the ability to initialize their registers from the bitstream contents. This can be done in a portable and standard way using an "initial" block in Verilog, and by affecting a value at the signal declaration in VHDL. This renders an explicit reset signal unnecessary in practice in some cases, which opens the way for further design optimization. However, this form of initialization is entirely not synthesizable for ASIC targets, and it is not easy to switch between the two forms of reset using V\*HDL.

2. V\*HDL support for composite types is very limited. Signals having a record type in VHDL are unidirectional, which makes them clumsy to use e.g. in bus interfaces. There is no record type support in Verilog, which means that a lot of copy-and-paste has to be done when forwarding grouped signals.

- 3. V\*HDL support for procedurally generated logic is extremely limited. The most advanced forms of procedural generation of synthesizable logic that V\*HDL offers are CPP-style directives in Verilog, combinatorial functions, and generate statements. Nothing really fancy, and it shows. To give a few examples:

- (a) Building highly flexible bus interconnect is not possible. Even arbitrating any given number of bus masters for commonplace protocols such as Wishbone is difficult with the tools that V\*HDL puts at our disposal.

- (b) Building a memory infrastructure (including bus interconnect, bridges and caches) that can automatically adapt itself at compile-time to any word size of the SDRAM is clumsy and tedious.

- (c) Building register banks for control, status and interrupt management of cores can also largely benefit from automation.

- (d) Many hardware acceleration problems can fit into the dataflow programming model. Manual dataflow implementation in V\*HDL has, again, a lot of redundancy and potential for human errors. See the Milkymist texture mapping unit [mthesis] [mxcell] for an example of this. The amount of detail to deal with manually also makes the design space exploration difficult, and therefore hinders the design of efficient architectures.

- (e) Pre-computation of values, such as filter coefficients for DSP or even simply trigonometric tables, must often be done using external tools whose results are copy-and-pasted (in the best cases, automatically) into the V\*HDL source.

Enter Migen, a Python toolbox for building complex digital hardware. We could have designed a brand new programming language, but that would have been reinventing the wheel instead of being able to benefit from Python's rich features and immense library. The price to pay is a slightly cluttered syntax at times when writing descriptions in FHDL, but we believe this is totally acceptable, particularly when compared to VHDL ;-)

Migen is made up of several related components, which are described in this manual.

# 1.2 Installing Migen

Either run the setup.py installation script or simply set PYTHONPATH to the root of the source directory.

For simulation support, an extra step is needed. See Installing the VPI module.

# 1.3 Feedback

Feedback concerning Migen or this manual should be sent to the Milkymist developers' mailing list at devel@lists.milkymist.org.

# THE FHDL LAYER